CAT1163 查看數據表(PDF) - Catalyst Semiconductor => Onsemi

零件编号

产品描述 (功能)

生产厂家

CAT1163

CAT1163 Datasheet PDF : 12 Pages

| |||

PIN DESCRIPTIONS

WDI: WATCHDOG INPUT

If there is no transition on the WDI for more than 1.6

seconds, the watchdog timer times out.

WP: WRITE PROTECT

If the pin is tied to VCC the entire memory array

becomes Write Protected (READ only). When the pin

is tied to GND or left floating normal read/write

operations are allowed to the device.

RESET/RESET: RESET I/O

These are open drain pins and can be used as reset

trigger inputs. By forcing a reset condition on the pins

the device will initiate and maintain a reset condition.

The RESET pin must be connected through a pull-

down resistor and the RESET pin must be connected

through a pull-up resistor.

SDA: SERIAL DATA ADDRESS

The bidirectional serial data/address pin is used to

transfer all data into and out of the device. The SDA

pin is an open drain output and can be wire-ORed

with other open drain or open collector outputs.

SCL: SERIAL CLOCK

Serial clock input.

DEVICE OPERATION

Reset Controller Description

The CAT1163 precision RESET controller ensures

correct system operation during brownout and power

up/down conditions. It is configured with open drain

CAT1163

RESET outputs. During power-up, the RESET outputs remain

active until VCC reaches the VTH threshold and will continue

driving the outputs for approximately 200ms (tPURST) after

reaching VTH. After the tPURST timeout interval, the device will

cease to drive the reset outputs. At this point the reset

outputs will be pulled up or down by their respective pull up/

down resistors. During power-down, the RESET outputs will

be active when VCC falls below VTH. The RESET outputs will

be valid so long as VCC is >1.0V (VRVALID).

The RESET pins are I/Os; therefore, the CAT1163 can act as

a signal conditioning circuit for an externally applied reset.

The inputs are edge triggered; that is, the RESET input in the

CAT1163 will initiate a reset timeout after detecting a low to

high transition and the RESET input in the CAT1163 will

initiate a reset timeout after detecting a high to low transition.

Watchdog Timer

The Watchdog Timer provides an independent protection for

microcontrollers. During a system failure, the CAT1163 will

respond with a reset signal after a time-out interval of 1.6

seconds for a lack of activity. The CAT1163 is designed with

a WDI input pin for the Watchdog Timer function. If the

microcontroller does not toggle the WDI input pin within 1.6

seconds, the Watchdog Timer times out. This will generate

a reset condition on reset outputs. The Watchdog Timer is

cleared by any transition on WDI.

As long as the reset signal is asserted, the Watchdog Timer

will not count and will stay cleared.

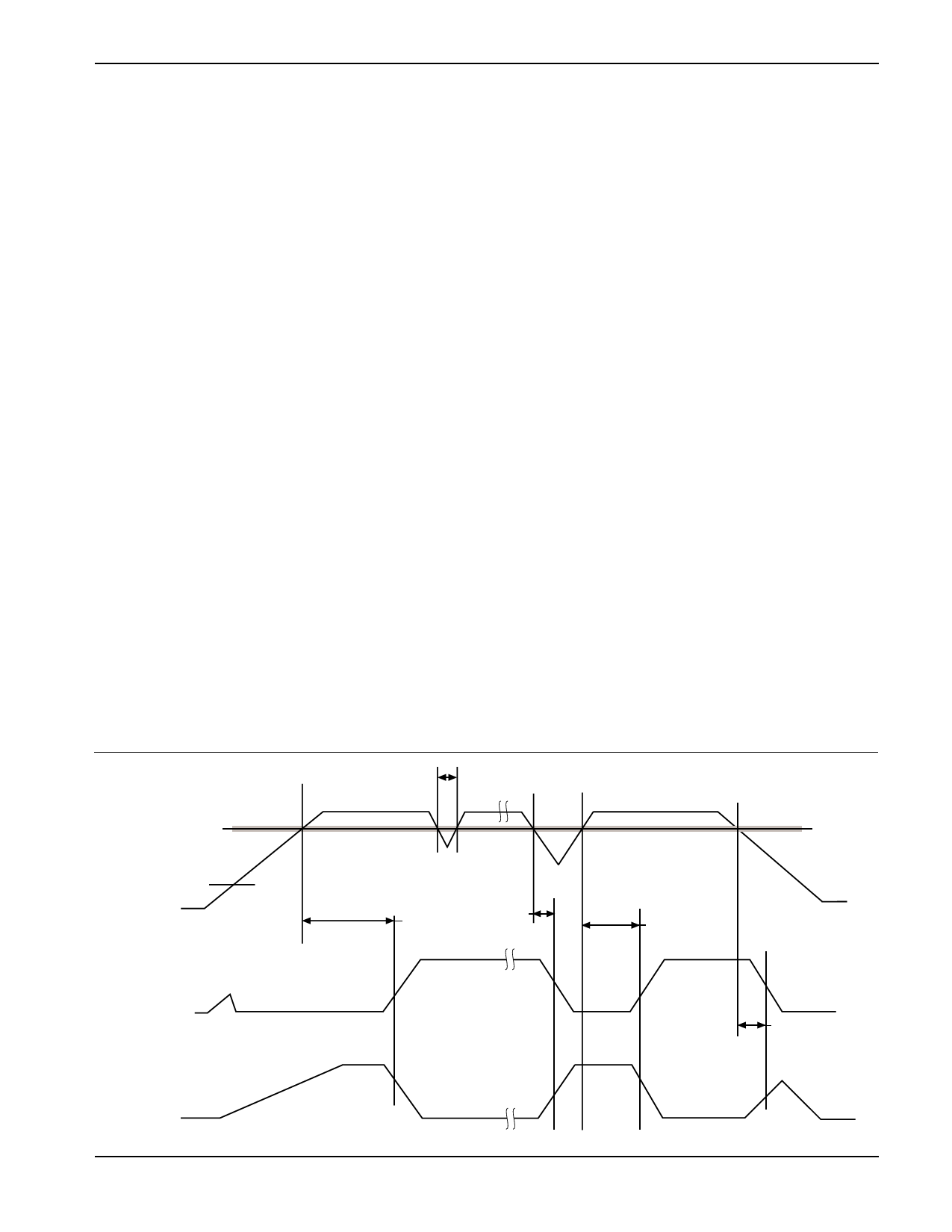

Figure 1. RESET Output Timing

t

GLITCH

VTH

VRVALID

VCC

tPURST

t RPD

tPURST

RESET

t RPD

RESET

5

Doc No. 3003, Rev. C