UPD720133GB-YEU-A 查看數據表(PDF) - NEC => Renesas Technology

零件编号

产品描述 (功能)

生产厂家

UPD720133GB-YEU-A Datasheet PDF : 40 Pages

| |||

µPD720133

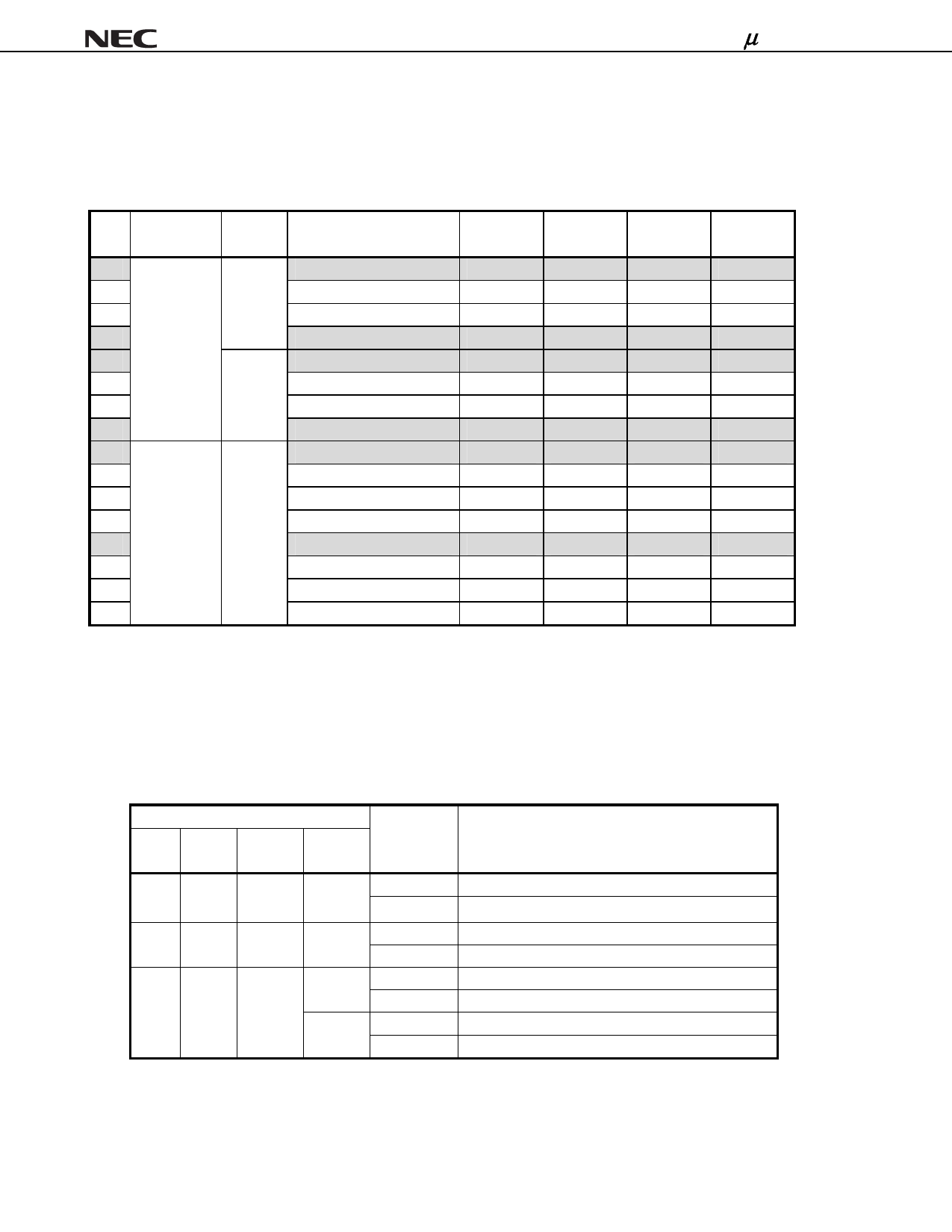

2.3 Control Bit in Serial ROM

The following tables show IDE status and control bit in serial ROM.

Table 2-3. DV1/DV0, CLC, PWR Setting

No.

Device

Internal

ATA/ATAPI

PWR

CLC

DV1

DV0

Power

Clock

0

Bus Powered 7.5 MHz No device connected

1

1

1

1

1

ATA

1

1

1

0

2

ATAPI

1

1

0

1

3

Reserved

1

1

0

0

4

60 MHz No device connected

1

0

1

1

5

ATA

1

0

1

0

6

ATAPI

1

0

0

1

7

Reserved

1

0

0

0

8

Self Powered 60 MHz No device connected

0

1

1

1

9

Combo (ATA)

0

1

1

0

10

Combo (ATAPI)

0

1

0

1

11

Combo auto device detect

0

1

0

0

12

No device connected

0

0

1

1

13

ATA

0

0

1

0

14

ATAPI

0

0

0

1

15

Auto device detect

0

0

0

0

Remarks 1. Setting of no. 0, 3, 4, 7, 8, and 12 are not allowed.

2. For bus powered setting, some critical considerations such as power consumption for the total system

should be observed.

3. The slave device function cannot use Auto device detect.

Table 2-4. DV1/DV0, DCC Setting

Condition

DV1 DV0

Mode

Target

Device

DCC

setting in

Serial ROM

1

0

ATA

ATA

Reset

Set

0

1

ATAPI ATAPI

Reset

Set

0

0

Auto

ATA

Reset

device

Set

detect

ATAPI

Reset

Set

Remark PIO mode 0-4 are always enabled.

Description

Ultra, Multi Word DMA are disabled.

Ultra, Multi Word DMA are enabled.

Ultra DMA are disabled.

Ultra, Multi Word DMA are enabled.

Ultra, Multi Word DMA are disabled.

Ultra, Multi Word DMA are enabled.

Ultra DMA are disabled.

Ultra, Multi Word DMA are enabled.

8

Preliminary Data Sheet S17100EJ2V0DS