AN87C196KS 查看數據表(PDF) - Intel

零件编号

产品描述 (功能)

生产厂家

AN87C196KS Datasheet PDF : 34 Pages

| |||

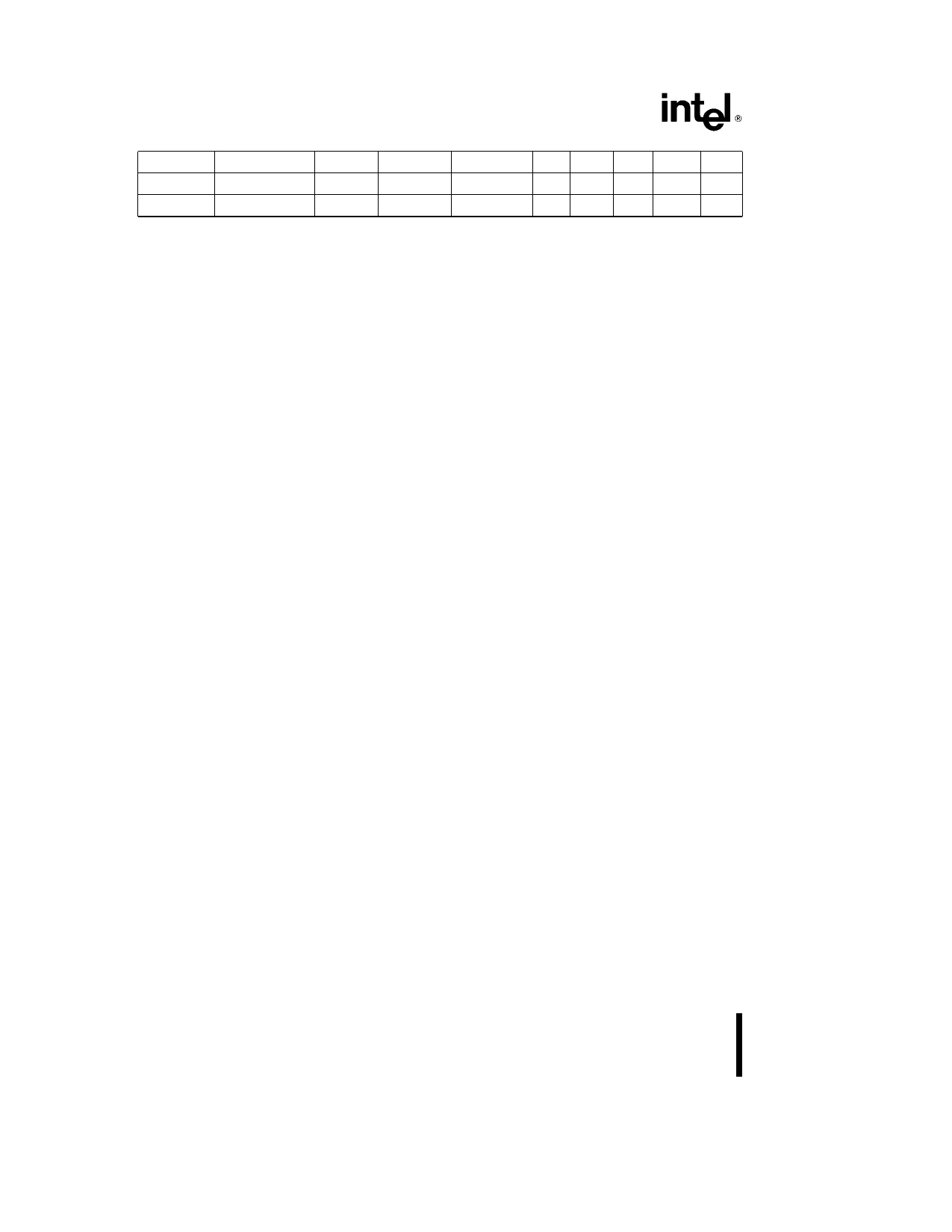

87C196KT 87C196KS

Device Pins Package EPROM Reg RAM Code RAM I O EPA SIO SSIO A D

87C196KT 68-Pin PLCC

32K

1K

512b

56 10 Y

Y

8

87C196KS 68-Pin PLCC

24K

1K

256b

56 10 Y

Y

8

NOTE

This is a PRODUCT PREVIEW DATA SHEET The AC and DC parameters contained within this data sheet may change

after full automotive temperature characterization of the device has been performed Contact your local sales office before

finalizing the Timing and D C characteristics of a design to verify you have the latest information

ARCHITECTURE

The KT KS are new members of the MCS-96 family

having the same architecture and use the same in-

struction set as the 80C196KB Many new features

have been added including

CPU FEATURES

Y Powerdown and Idle Modes

Y 16 MHz Operating Frequency

Y A High Performance Peripheral

Transaction Server (PTS)

Y 37 Interrupt Vectors

Y Up to 512 Bytes of Additional Code

RAM

Y Up to 1 Kbyte of Additional Register

RAM

Y ‘‘Windowing’’ Allows 8-Bit Addressing

to some 16-Bit Addresses

Y 1 75 ms 16 x 16 Multiply

Y 3 ms 32 16 Divide

Y Oscillator Fail Detect Circuitry

PERIPHERAL FEATURES

Programmable A D Conversion and S H Times

10 Capture Compare I O with 2 Flexible Timers

(250 ns Resolution and Double Buffered Inputs)

Synchronous Serial I O Port for Full Duplex Seri-

al I O

Synchronous Asynchronous Serial I O Port

(with Dedicated 16-Bit Baud Rate Generator)

Total Utilization of ALL Available Pins (I O Mux’d

with Control)

(2) 16-Bit Timers with Prescale Cascading and

Quadrature Counting Capabilities

Up to 12 Externally Triggered Interrupts

NEW INSTRUCTIONS

XCH XCHB Exchange the contents of two loca-

tions either Word or Byte is support-

ed

BMOVI

Interruptable Block Move Instruction

allows the user to be interrupted dur-

ing long executing Block Moves

TIJMP

Table Indirect JUMP This instruction

incorportes a way to do complex

CASE level branches through one in-

struction An example of such code

savings several interrupt sources and

only one interrupt vector The TIJMP

instruction will sort through the sourc-

es and branch to the appropriate sub-

code level in one instruction This in-

struction was added especially for the

EPA structure but has other code sav-

ing advantages

EPTS DPTS Enable and Disable Interrupts (Works

like EI and DI)

SFR OPERATION

A total of 1 Kbyte of Register RAM is implemented

on the 87C196KT KS devices These locations sup-

port the on-chip peripherals that the 87C196KT KS

has (SFR’s) as well as offering a data storage area

These locations are all 8-bit directly addressable by

use of the windowing technique Any 32- 64- or 128-

byte section can be relocated into the upper 32- 64-

or 128-byte area of the Register RAM area 080H –

0FFH

2

2