AT88SC0104C-PI 查看數據表(PDF) - Atmel Corporation

零件编号

产品描述 (功能)

生产厂家

AT88SC0104C-PI Datasheet PDF : 17 Pages

| |||

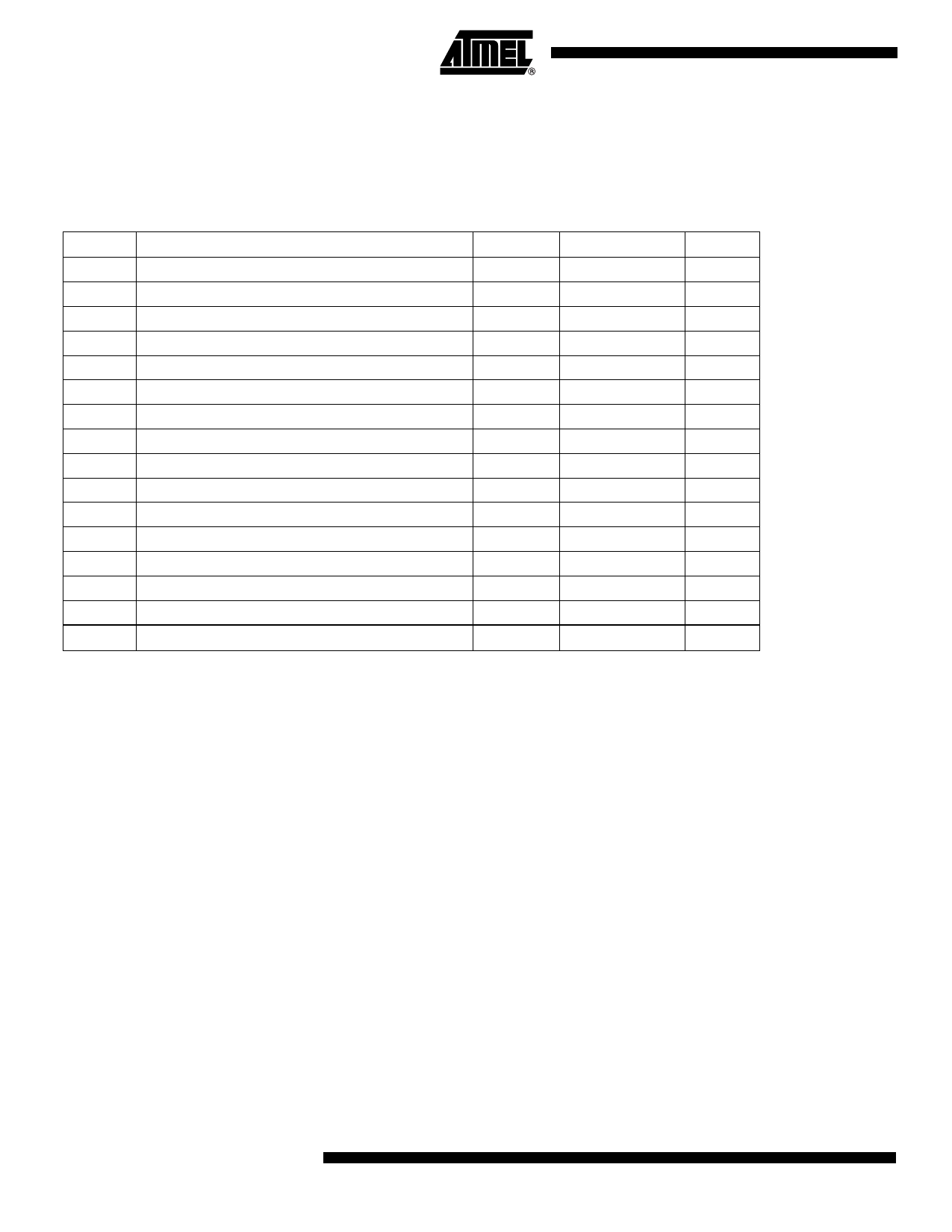

Table 3. AC Characteristics

Applicable over recommended operating range from VCC = +2.7 to 5.5V,

TAC = -40oC to +85oC, CL = 30pF (unless otherwise noted)

Symbol Parameter

Min

fCLK

Async Clock Frequency (VCC Range: +4.5 - 5.5V)

1

fCLK

Async Clock Frequency (VCC Range: +2.7 - 3.3V)

1

fCLK

Synch Clock Frequency

0

Clock Duty cycle

40

tR

Rise Time - I/O, RST

tF

Fall Time - I/O, RST

tR

Rise Time - CLK

tF

Fall Time - CLK

tAA

Clock Low to Data Out Valid

tHD.STA Start Hold Time

200

tSU.STA Start Set-up Time

200

tHD.DAT Data In Hold Time

10

tSU.DAT Data In Set-up Time

100

tSU.STO Stop Set-up Time

200

tDH

Data Out Hold Time

20

tWR

Write Cycle Time

Max

5

4

1

60

1

1

9% x period

9% x period

35

9

Units

MHz

MHz

MHz

%

uS

uS

uS

uS

nS

nS

nS

nS

nS

nS

nS

mS

Device Operation For

Synchronous

Protocols

CLOCK and DATA TRANSITIONS: The SDA pin is normally pulled high with an exter-

nal device. Data on the SDA pin may change only during SCL low time periods (see

Figure 4 on page 5). Data changes during SCL high periods will indicate a start or stop

condition as defined below.

START CONDITION: A high-to-low transition of SDA with SCL high is a start condition

which must precede any other command (see Figure 5 on page 6).

STOP CONDITION: A low-to-high transition of SDA with SCL high is a stop condition.

After a read sequence, the stop command will place the EEPROM in a standby power

mode (see Figure 5 on page 6).

ACKNOWLEDGE: All addresses and data words are serially transmitted to and from the

EEPROM in 8-bit words. The EEPROM sends a zero to acknowledge that it has

received each word. This happens during the ninth clock cycle.

MEMORY RESET: After an interruption in protocol, power loss or system reset, any 2-

wire part can be reset by following these steps:

1. Clock up to 9 cycles.

2. Look for SDA high in each cycle while SCL is high.

3. Create a start condition.

4 AT88SC0104C

2021GS–SMEM–7/06