N25Q128A23EF8H0G 查看數據表(PDF) - Numonyx -> Micron

零件编号

产品描述 (功能)

生产厂家

N25Q128A23EF8H0G

N25Q128A23EF8H0G Datasheet PDF : 180 Pages

| |||

N25Q128 - 3 V

Description

The memory can be write protected by software using a mix of volatile and non-volatile

protection features, depending on the application needs. The protection granularity is of 64-

Kbyte (sector granularity) for volatile protections.

The N25Q128 has 64 one-time-programmable bytes (OTP bytes) that can be read and

programmed using two dedicated instructions, Read OTP (ROTP) and Program OTP

(POTP), respectively. These 64 bytes can be permanently locked by a particular Program

OTP (POTP) sequence. Once they have been locked, they become read-only and this state

cannot be reversed.

Many different N25Q128 configurations are available, please refer to the ordering scheme

page for the possibilities. Additional features are available as security options (The Security

features are described in a dedicated Application Note). Please contact your nearest

Numonyx Sales office for more information.

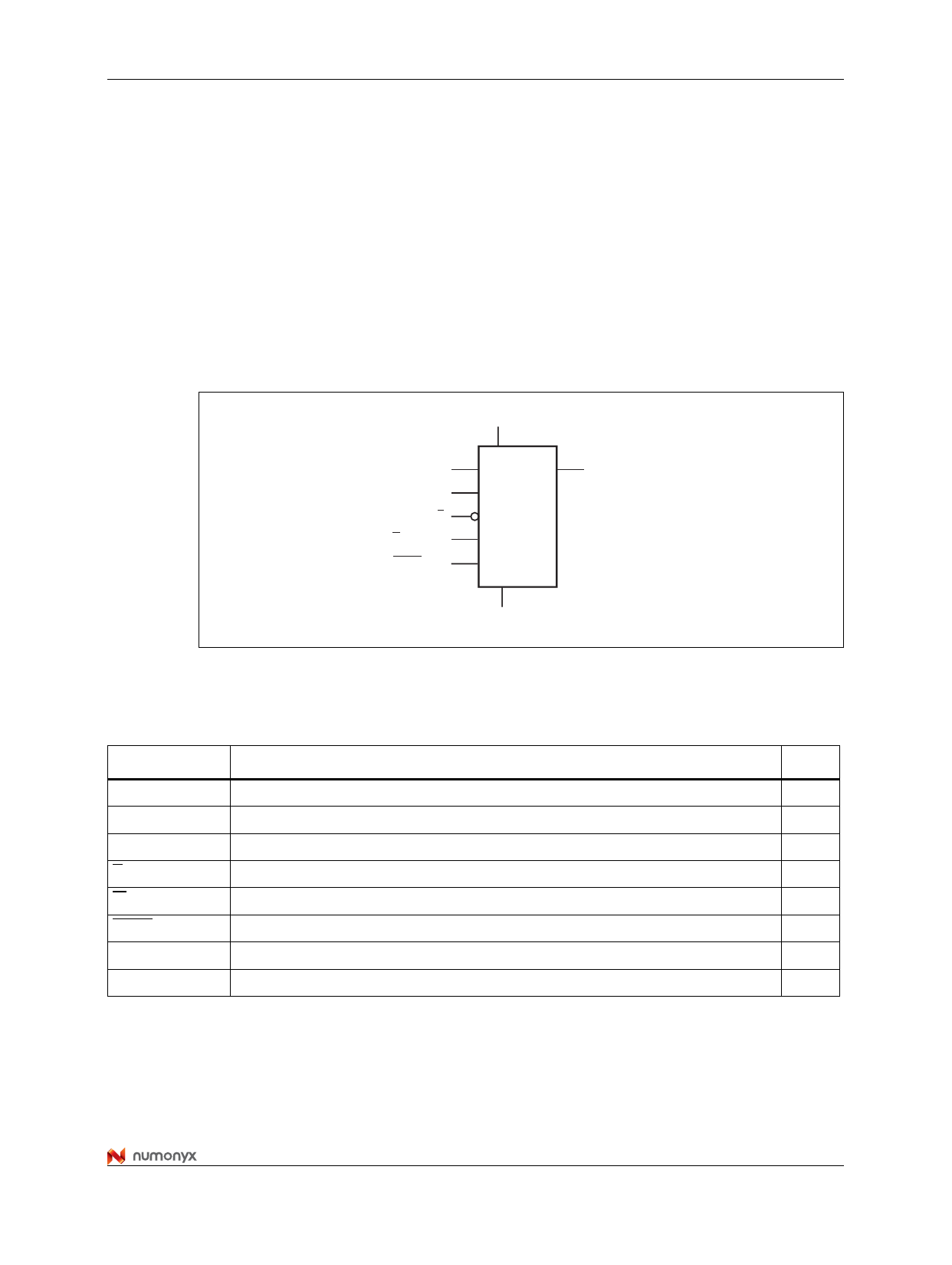

Figure 1. Logic diagram

VCC

DQ0

DQ1

C

S

W/VPP/DQ2

HOLD/DQ3

Note:

VSS

Logic_Diagram_x25x

Reset functionality is available in devices with a dedicated part number. See Section 16:

Ordering information.

Table 1. Signal names

Signal

Description

I/O

C

DQ0

DQ1

Serial Clock

Serial Data input

Serial Data output

Input

I/O(1)

I/O(2)

S

W/VPP/DQ2

HOLD/DQ3(4)

Chip Select

Write Protect/Enhanced Program supply voltage/additional data I/O

Hold (Reset function available upon customer request)/additional data I/O

Input

I/O(3)

I/O(3)

VCC

Supply voltage

–

VSS

Ground

–

1. Provides dual and quad I/O for Extended SPI protocol instructions, dual I/O for Dual I/O SPI protocol instructions, and

quad I/O for Quad I/O SPI protocol instructions.

2. Provides dual and quad instruction input for Extended SPI protocol, dual instruction input for Dual I/O SPI protocol, and

quad instruction input for Quad I/O SPI protocol.

3. Provides quad I/O for Extended SPI protocol instructions, and quad I/O for Quad I/O SPI protocol instructions.

4. Reset functionality available with a dedicated part number. See Section 16: Ordering information.

13/180