DP8051_07 查看數據表(PDF) - Digital Core Design

零件编号

产品描述 (功能)

生产厂家

DP8051_07 Datasheet PDF : 10 Pages

| |||

UARTs, and interrupts to be processed in full

speed mode if enabled. It is very desired when

microcontroller is planned to use in portable

and power critical applications.

DoCD™ Debug Unit – it’s a real-time hard-

ware debugger provides debugging capability

of a whole SoC system. In contrast to other on-

chip debuggers DoCD™ provides non-intrusive

debugging of running application. It can halt,

run, step into or skip an instruction, read/write

any contents of microcontroller including all

registers, internal, external, program memo-

ries, all SFRs including user defined peripher-

als. Hardware breakpoints can be set and con-

trolled on program memory, internal and exter-

nal data memories, as well as on SFRs. Hard-

ware breakpoint is executed if any write/read

occurred at particular address with certain data

pattern or without pattern. Two additional pins

CODERUN, DEBUGACS indicate the sate of

the debugger and CPU. CODERUN is active

when CPU is executing an instruction. DE-

BUGACS pin is active when any access is per-

formed by DoCD™ debugger. The DoCD™

system includes JTAG interface and complete

set of tools to communicate and work with core

in real time debugging. It is built as scalable

unit and some features can be turned off to

save silicon and reduce power consumption. A

special care on power consumption has been

taken, and when debugger is not used it is

automatically switched in power save mode.

Finally whole debugger is turned off when de-

bug option is no longer used.

PROGRAM CODE SPACE

IMPLEMENTATION

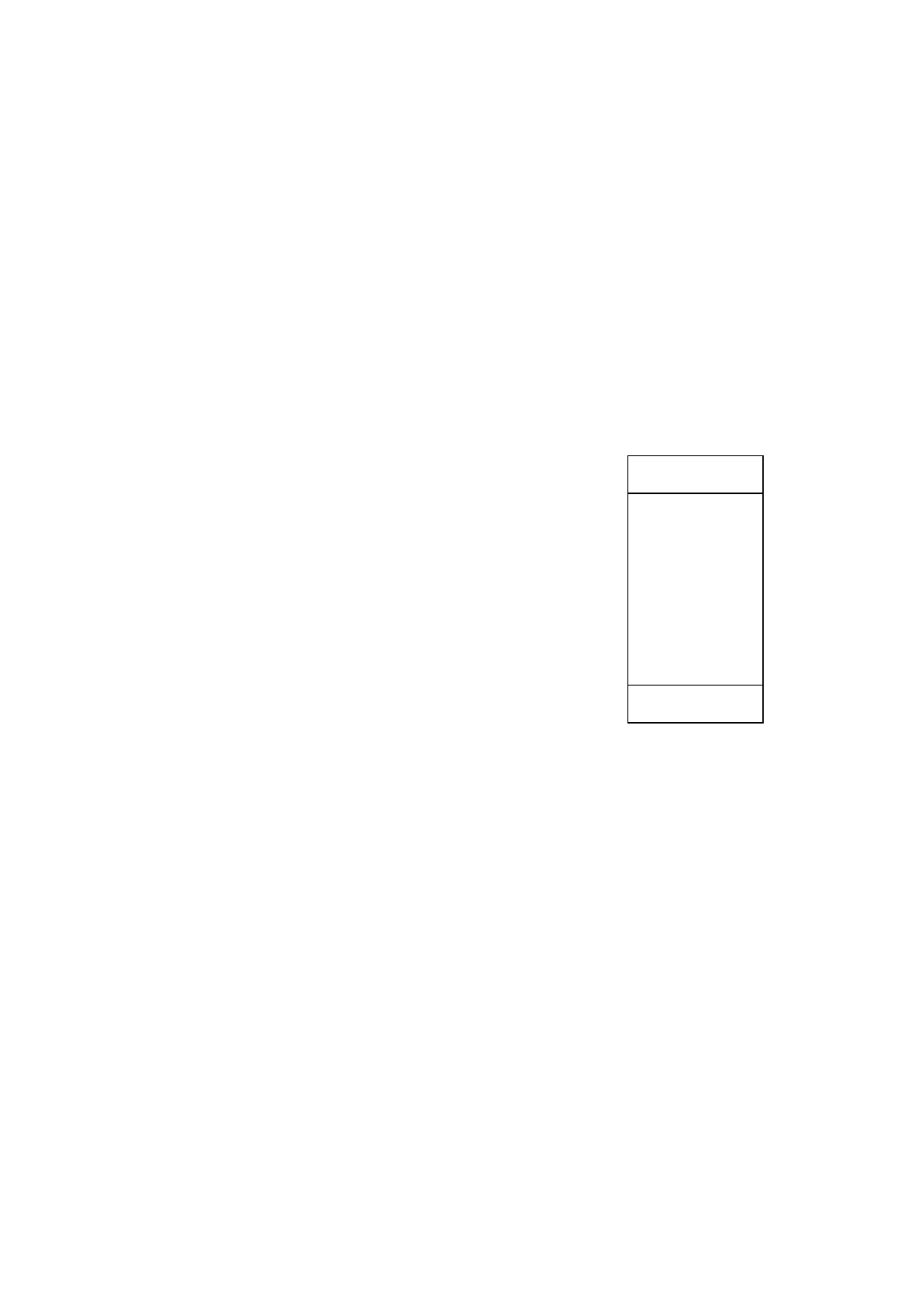

The figure below shows an example Pro-

gram Memory space implementation in sys-

tems with DP8051CPU Microcontroller core.

The On-chip Program Memory located in ad-

dress space between 0kB and 1kB is typically

used for BOOT code with system initialization

functions. This part of the code is typically im-

plemented as ROM. The On-chip Program

Memory located in address space between

60kB and 64kB is typically used for timing criti-

cal part of the code e.g. interrupt subroutines,

arithmetic functions etc. This part of the code is

typically implemented as RAM and can be

loaded by the BOOT code during initialization

phase from Off-chip memory or through RS232

interface from external device. From the two

mentioned above spaces program code is

All trademarks mentioned in this document

are trademarks of their respective owners.

executed without wait-states and can achieve

a top performance up to 200 million instruc-

tions per second (many instructions executed

in one clock cycle). The Off-chip Program

Memory located in address space between

1kB and 60kB is typically used for main code

and constants. This part of the code is usually

implemented as ROM, SRAM or FLASH de-

vice. Because of relatively long access time

the program code executed from mentioned

above devices must be fetched with additional

Wait-States. Number of required Wait-States

depends on memory access time and

DP8051CPU clock frequency. In most cases

the proper number of Wait-States cycles is

between 2-5. The READY pin can be also dy-

namically modulated e.g. by SDRAM control-

ler.

0xFFFF

0xF000

On chip Memory

(implemented as RAM)

Off chip Memory

(implemented as ROM,

SRAM or FLASH)

0x0400

0x0000

On-chip Memory

(implemented as ROM)

The figure below shows a typical Program

Memories connections in system with

DP8051CPU Microcontroller core.

http://www.DigitalCoreDesign.com

http://www.dcd.pl

Copyright 1999-2007 DCD – Digital Core Design. All Rights Reserved.