MFRC522_(2007) 查看數據表(PDF) - NXP Semiconductors.

零件编号

产品描述 (功能)

生产厂家

MFRC522_ Datasheet PDF : 109 Pages

| |||

NXP Semiconductors

MFRC522

Contactless Reader IC

Table 4: Communication overview for ISO/IEC 14443A/MIFARE® reader/writer …continued

Communication

direction

transfer

speed

ISO/IEC 14443A/ MIFARE®

106 kbit/s

212 kbit/s 424 kbit/s

848 kbit/s

Card → Reader

(MFRC522

receives data from

a card)

modulation

on card side

subcarrier

frequency

subcarrier

load

modulation

subcarrier

load

modulation

subcarrier

load

modulation

subcarrier

load

modulation

13.56 MHz/16 13.56MHz/16 13.56MHz/16 13.56MHz/16

bit coding

Manchester

coding

BPSK

BPSK

BPSK

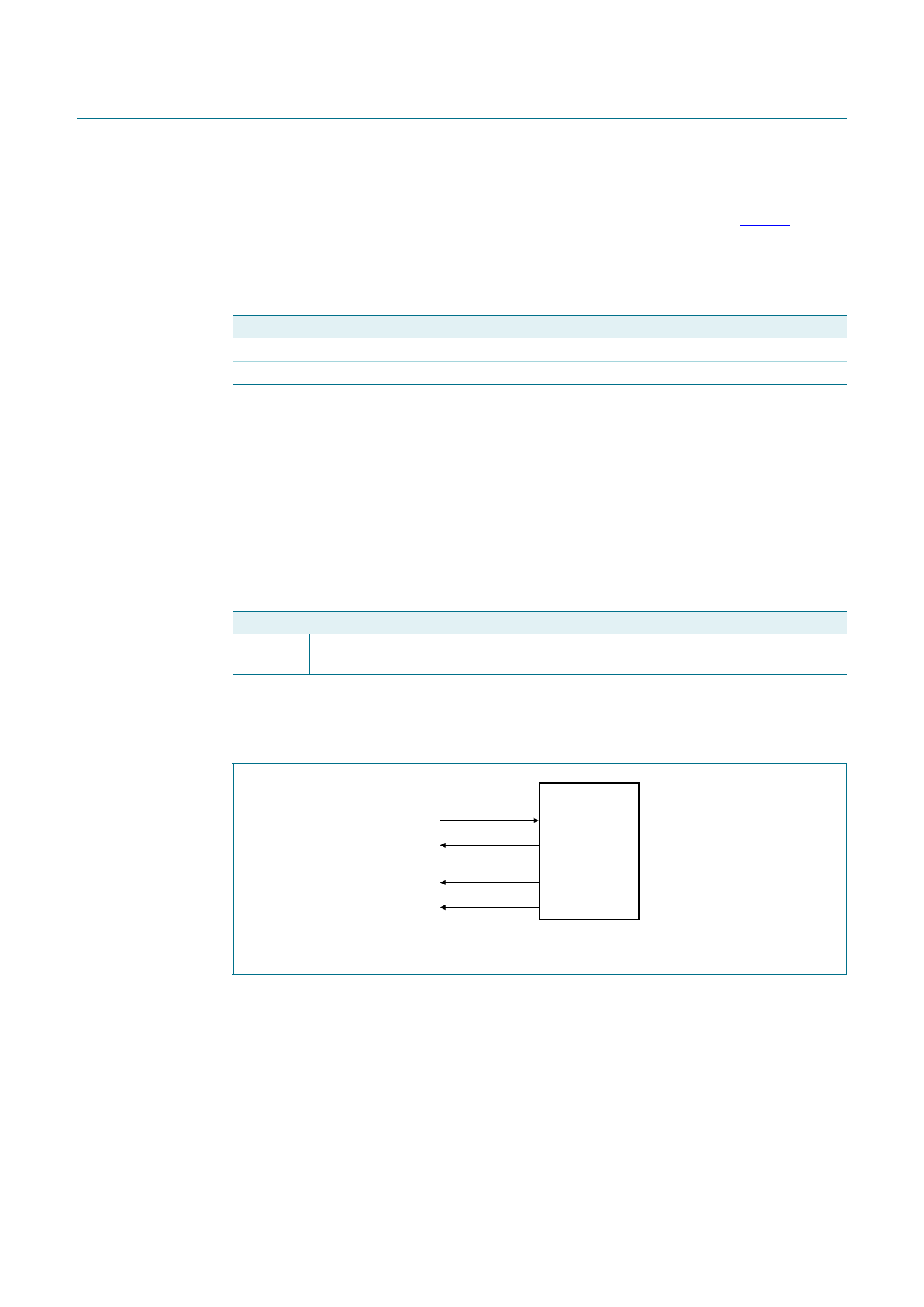

The contactless UART of MFRC522 and a dedicated external host are required to handle

the complete MIFARE® / ISO/IEC 14443A / MIFARE® protocol. The following Figure 6

“Data Coding and framing according to ISO/IEC 14443A.” shows the Data Coding and

framing according to ISO/IEC 14443A / MIFARE®.

ISO14443-A Framing at 106 kbit/s

Start

8 bit data

8 bit data

8 bit data

odd

Start Bit is "1"

Par

odd

Par

odd

Par

ISO14443-A Framing at 212, 424 and 848 kbit/s

Start

8 bit data

8 bit data

Burst of Start Bit is "0"

odd

Par

32 sub-

carrier

clocks

8 bit data

even

Par.

odd

Par Even parity at the

end of the frame!

Fig 6. Data Coding and framing according to ISO/IEC 14443A.

The internal CRC co-processor calculates the CRC value according to the definitions

given in the ISO/IEC 14443A part 3 and handles parity generation internally according to

the transfer speed. Automatic parity generation can be switched off by bit ParityDisable in

register 0x1D ManualRCVReg.

112132

Product data sheet

Rev. 3.2 — 22 May 2007

© NXP B.V. 2007. All rights reserved.

10 of 109