FM24C04B-G 查看數據表(PDF) - Cypress Semiconductor

零件编号

产品描述 (功能)

生产厂家

FM24C04B-G Datasheet PDF : 13 Pages

| |||

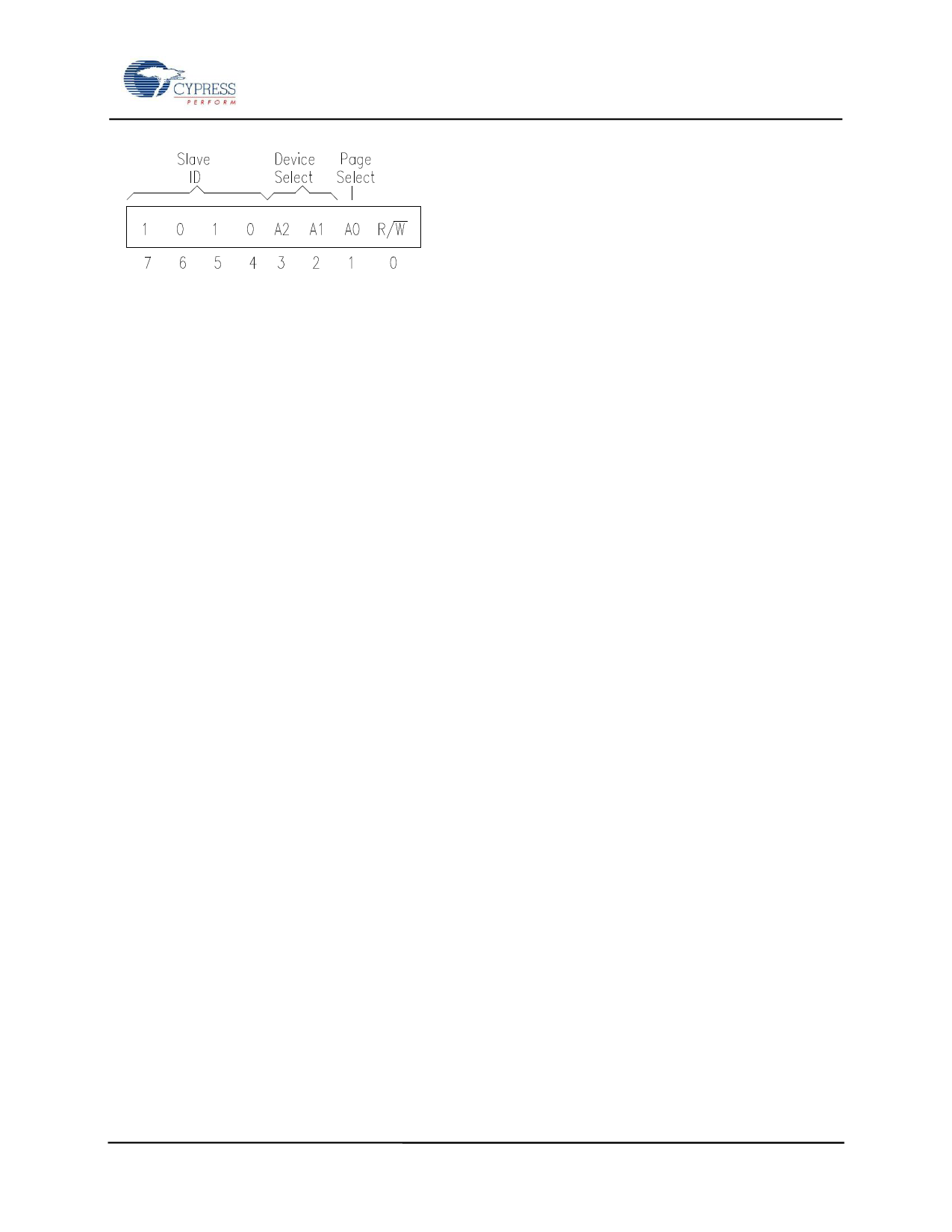

Figure 4. Slave Address

No word address occurs for a read operation. Reads

always use the lower 8-bits that are held internally in

the address latch and the 9th address bit is part of the

slave address. Reads always begin at the address

following the previous access. A random read address

can be loaded by doing a write operation as explained

below.

After transmission of each data byte, just prior to the

acknowledge, the FM24C04B increments the internal

address latch. This allows the next sequential byte to

be accessed with no additional addressing. After the

last address (1FFh) is reached, the address latch will

roll over to 000h. There is no limit to the number of

bytes that can be accessed with a single read or write

operation.

Data Transfer

After all address information has been transmitted,

data transfer between the bus master and the

FM24C04B can begin. For a read operation the

FM24C04B will place 8 data bits on the bus then wait

for an acknowledge. If the acknowledge occurs, the

next sequential byte will be transferred. If the

acknowledge is not sent, the read operation is

concluded. For a write operation, the FM24C04B will

accept 8 data bits from the master then send an

acknowledge. All data transfer occurs MSB (most

significant bit) first.

FM24C04B

Memory Operation

The FM24C04B is designed to operate in a manner

very similar to other 2-wire interface memory

products. The major differences result from the

higher performance write capability of FRAM

technology. These improvements result in some

differences between the FM24C04B and a similar

configuration EEPROM during writes. The complete

operation for both writes and reads is explained

below.

Write Operation

All writes begin with a slave address then a word

address. The bus master indicates a write operation

by setting the LSB of the Slave address to a 0. After

addressing, the bus master sends each byte of data to

the memory and the memory generates an

acknowledge condition. Any number of sequential

bytes may be written. If the end of the address range

is reached internally, the address counter will wrap

from 1FFh to 000h.

Unlike other nonvolatile memory technologies, there

is no write delay with FRAM. The entire memory

cycle occurs in less time than a single bus clock.

Therefore any operation including read or write can

occur immediately following a write. Acknowledge

polling, a technique used with EEPROMs to

determine if a write is complete is unnecessary and

will always return a done condition.

An actual memory array write occurs after the 8th

data bit is transferred. It will be complete before the

acknowledge is sent. Therefore if the user desires to

abort a write without altering the memory contents,

this should be done using a start or stop condition

prior to the 8th data bit. The FM24C04B needs no

page buffering.

The memory array can be write protected using the

WP pin. Pulling WP high will disable writes to the

entire array. The FM24C04B will not acknowledge

data bytes that are written when write protect is

asserted. In addition, the address counter will not

increment if writes are attempted. Pulling WP low

(VSS) will deactivate this feature.

Figures 5 and 6 below illustrate both a single-byte

and multiple- byte write cases.

Document Number: 001-84446 Rev. *A

Page 5 of 13