W77E468 查看數據表(PDF) - Winbond

零件编号

产品描述 (功能)

生产厂家

W77E468 Datasheet PDF : 84 Pages

| |||

Preliminary W77E468

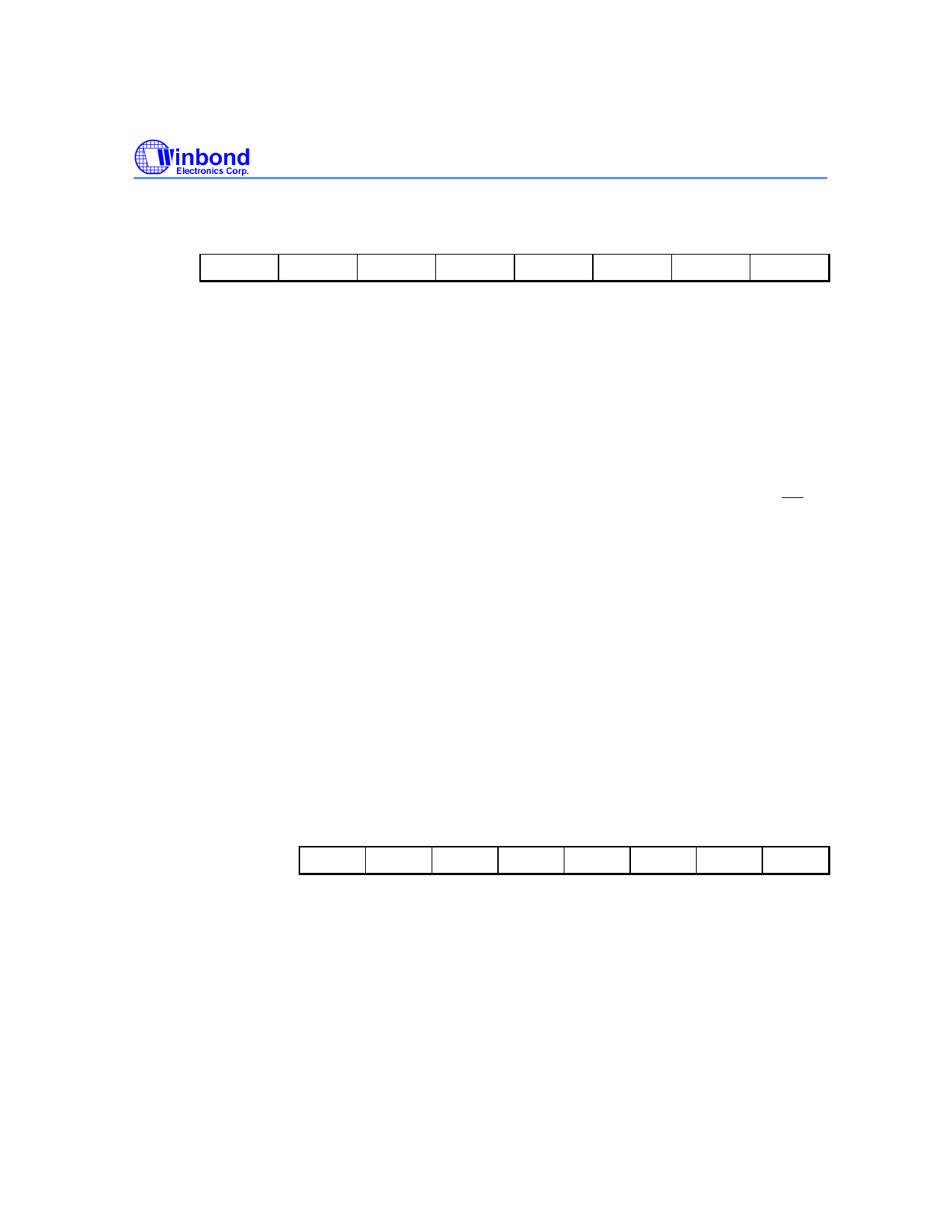

STATUS REGISTER

Bit:

7

-

6

5

4

3

2

1

0

HIP

LIP

XTUP SPTA1 SPRA1 SPTA0 SPRA0

Mnemonic: STATUS

Address: C5h

HIP: High Priority Interrupt Status. When set, it indicates that software is servicing a high priority

interrupt. This bit will be cleared when the program executes the corresponding RETI

instruction.

LIP: Low Priority Interrupt Status. When set, it indicates that software is servicing a low priority

interrupt. This bit will be cleared when the program executes the corresponding RETI

instruction.

XTUP:Crystal Oscillator Warm-up Status. when set, this bit indicates the crystal oscillator has

completed the 65536 clocks warm-up delay. Each time the crystal oscillator is restarted by exit

from power down mode or the XTOFF bit is set, hardware will clear this bit. This bit is set to 1

after a power-on reset. When this bit is cleared, it prevents software from setting the XT/ RG bit

to enable CPU operation from crystal oscillator.

SPTA1:Serial Port 1 Transmit Activity. This bit is set during serial port 1 is currently transmitting data.

It is cleared when TI_1 bit is set by hardware. Changing the Clock Divide Control bits

CD0,CD1 will be ignored when this bit is set to 1 and SWB = 1.

SPRA1:Serial Port 1 Receive Activity. This bit is set during serial port 1 is currently receiving a data.

It is cleared when RI_1 bit is set by hardware. Changing the Clock Divide Control bits

CD0,CD1 will be ignored when this bit is set to 1 and SWB = 1.

SPTA0:Serial Port 0 Transmit Activity. This bit is set during serial port 0 is currently transmitting data.

It is cleared when TI bit is set by hardware. Changing the Clock Divide Control bits CD0,CD1

will be ignored when this bit is set to 1 and SWB = 1.

SPRA0:Serial Port 0 Receive Activity. This bit is set during serial port 0 is currently receiving a data.

It is cleared when RI bit is set by hardware. Changing the Clock Divide Control bits CD0,CD1

will be ignored when this bit is set to 1 and SWB = 1.

TIMED ACCESS

Bit:

7

6

5

4

3

2

1

0

TA.7 TA.6 TA.5 TA.4 TA.3 TA.2 TA.1 TA.0

Mnemonic: TA

Address: C7h

TA: The Timed Access register controls the access to protected bits. To access protected bits, the

user must first write AAH to the TA. This must be immediately followed by a write of 55H to TA.

Now a window is opened in the protected bits for three machine cycles, during which the user

can write to these bits.

- 25 -

Publication Release Date: January 1999

Revision A1