M48T35 وں¥çœ‹و•¸و“ڑè،¨ï¼ˆPDF) - STMicroelectronics

零ن»¶ç¼–هڈ·

ن؛§ه“پوڈڈè؟° (هٹں能)

ç”ںن؛§هژ‚ه®¶

M48T35 Datasheet PDF : 26 Pages

| |||

M48T35, M48T35Y

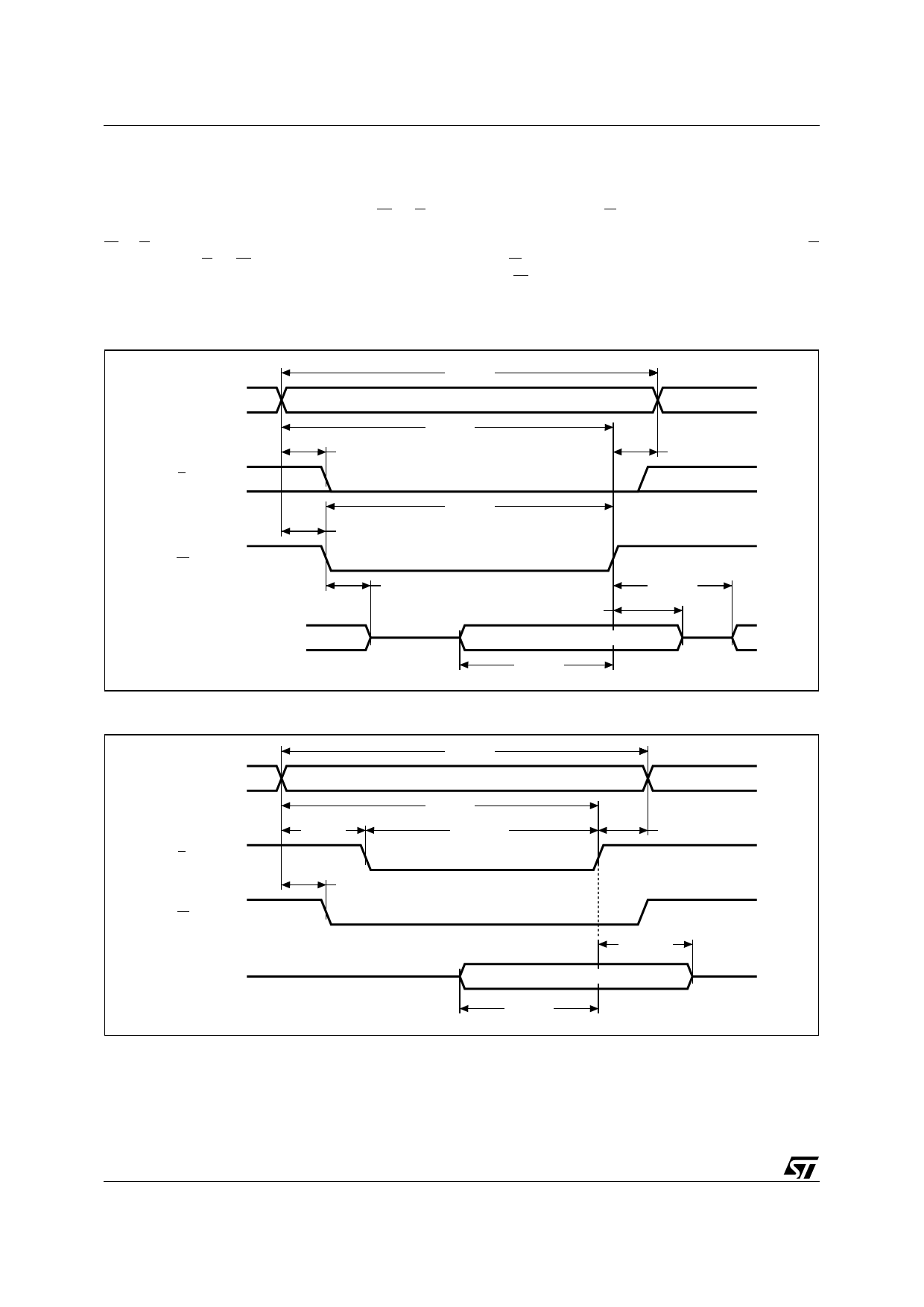

WRITE Mode

The M48T35/Y is in the WRITE Mode whenever W

and E are low. The start of a WRITE is referenced

from the latter occurring falling edge of W or E. A

WRITE is terminated by the earlier rising edge of

W or E. The addresses must be held valid through-

out the cycle. E or W must return high for a mini-

mum of tEHAX from Chip Enable or tWHAX from

WRITE Enable prior to the initiation of another

READ or WRITE Cycle. Data-in must be valid tD-

VWH prior to the end of WRITE and remain valid for

tWHDX afterward. G should be kept high during

WRITE Cycles to avoid bus contention; although,

if the output bus has been activated by a low on E

and G, a low on W will disable the outputs tWLQZ

after W falls.

Figure 8. WRITE Enable Controlled, WRITE AC Waveform

A0-A14

E

tAVEL

tAVWL

tAVAV

VALID

tAVWH

tWLWH

W

DQ0-DQ7

tWLQZ

tWHDX

DATA INPUT

tDVWH

tWHAX

tWHQX

AI00926

Figure 9. Chip Enable Controlled, WRITE AC Waveforms

tAVAV

A0-A14

VALID

tAVEL

tAVEH

tELEH

E

tAVWL

tEHAX

W

tEHDX

DQ0-DQ7

DATA INPUT

tDVEH

AI00927

8/26