MB90352 查看數據表(PDF) - Cypress Semiconductor

零件编号

产品描述 (功能)

生产厂家

MB90352 Datasheet PDF : 83 Pages

| |||

MB90350 Series

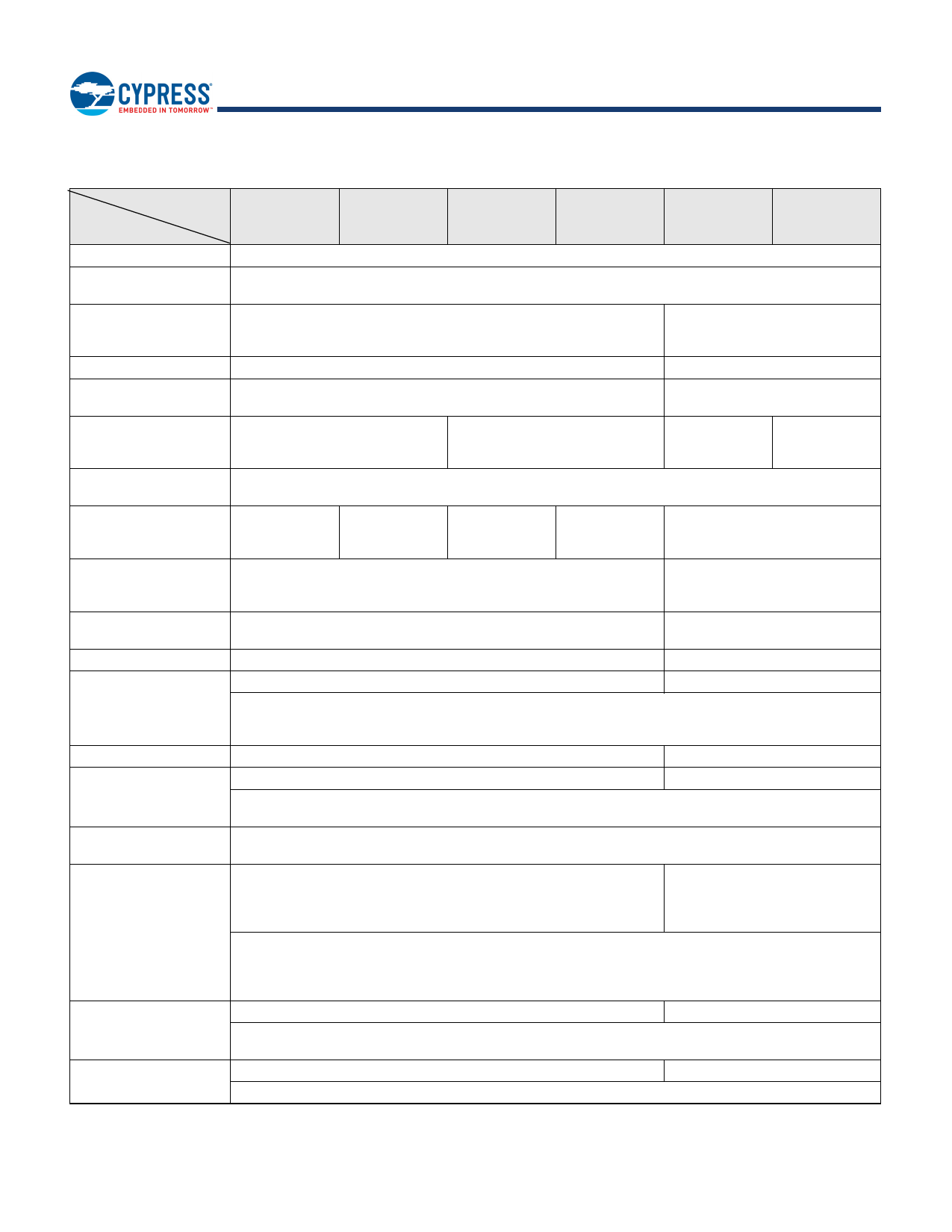

2. Product Lineup 2

Part Number

Parameter

CPU

MB90351A,

MB90352A

MB90351TA,

MB90352TA

MB90351AS, MB90351TAS,

MB90352AS MB90352TAS

F2MC-16LX CPU

MB90V340A-

101

MB90V340A-

102

System clock

On-chip PLL clock multiplier (×1, ×2, ×3, ×4, ×6, 1/2 when PLL stops)

Minimum instruction execution time : 42 ns (oscillation clock 4 MHz, PLL × 6)

ROM

MASK ROM

64Kbytes :MB90351A(S), MB90351TA(S)

128Kbytes :MB90352A(S), MB90352TA(S)

External

RAM

4 Kbytes

30 Kbytes

Emulator-specific power

supply*

—

Yes

Sub clock pin

(X0A, X1A)

Yes

(Max 100 kHz)

No

No

Yes

Clock monitor

function

No

Low voltage/CPU

operation detection

No

Yes

No

Yes

No

reset

Operating

voltage range

3.5 V to 5.5 V : at normal operating (not using A/D converter)

4.0 V to 5.5 V : at using A/D converter

4.5 V to 5.5 V : at using external bus

5 V 10%

Operating

temperature range

40 °C to 125 °C

—

Package

LQFP-64

PGA-299

2 channels

5 channels

UART

I2C (400 Kbps)

Wide range of baud rate settings using a dedicated reload timer

Special synchronous options for adapting to different synchronous serial protocols

LIN functionality working either as master or slave LIN device

1 channel

2 channels

A/D Converter

16-bit Reload Timer

(4 channels)

15 channels

24 channels

10-bit or 8-bit resolution

Conversion time : Min 3 s includes sample time (per one channel)

Operation clock frequency : fsys/21, fsys/23, fsys/25 (fsys Machine clock frequency)

Supports External Event Count function.

16-bit I/O Timer

(2 channels)

I/O Timer 0 (clock input FRCK0) corresponds to ICU 0/1.

I/O Timer 1 (clock input FRCK1) corresponds to

ICU 4/5/6/7, OCU 4/5/6/7.

I/O Timer 0 corresponds to ICU

0/1/2/3, OCU 0/1/2/3.

I/O Timer 1 corresponds to ICU

4/5/6/7, OCU 4/5/6/7.

Signals an interrupt when overflowing.

Supports Timer Clear when a match with Output Compare (Channel 0, 4) .

Operation clock frequency : fsys, fsys/21, fsys/22, fsys/23, fsys/24, fsys/25, fsys/26, fsys/27

(fsys Machine clock frequency)

16-bit Output

Compare

4 channels

Signals an interrupt when 16-bit I/O Timer matches output compare registers.

A pair of compare registers can be used to generate an output signal.

8 channels

16-bit Input Capture

6 channels

8 channels

Retains freerun timer value by (rising edge, falling edge or rising & falling edge), signals an interrupt.

(Continued)

Document Number: 002-07872 Rev. *A

Page 6 of 83