LP62S4096E-T 查看數據表(PDF) - AMIC Technology

零件编号

产品描述 (功能)

生产厂家

LP62S4096E-T Datasheet PDF : 12 Pages

| |||

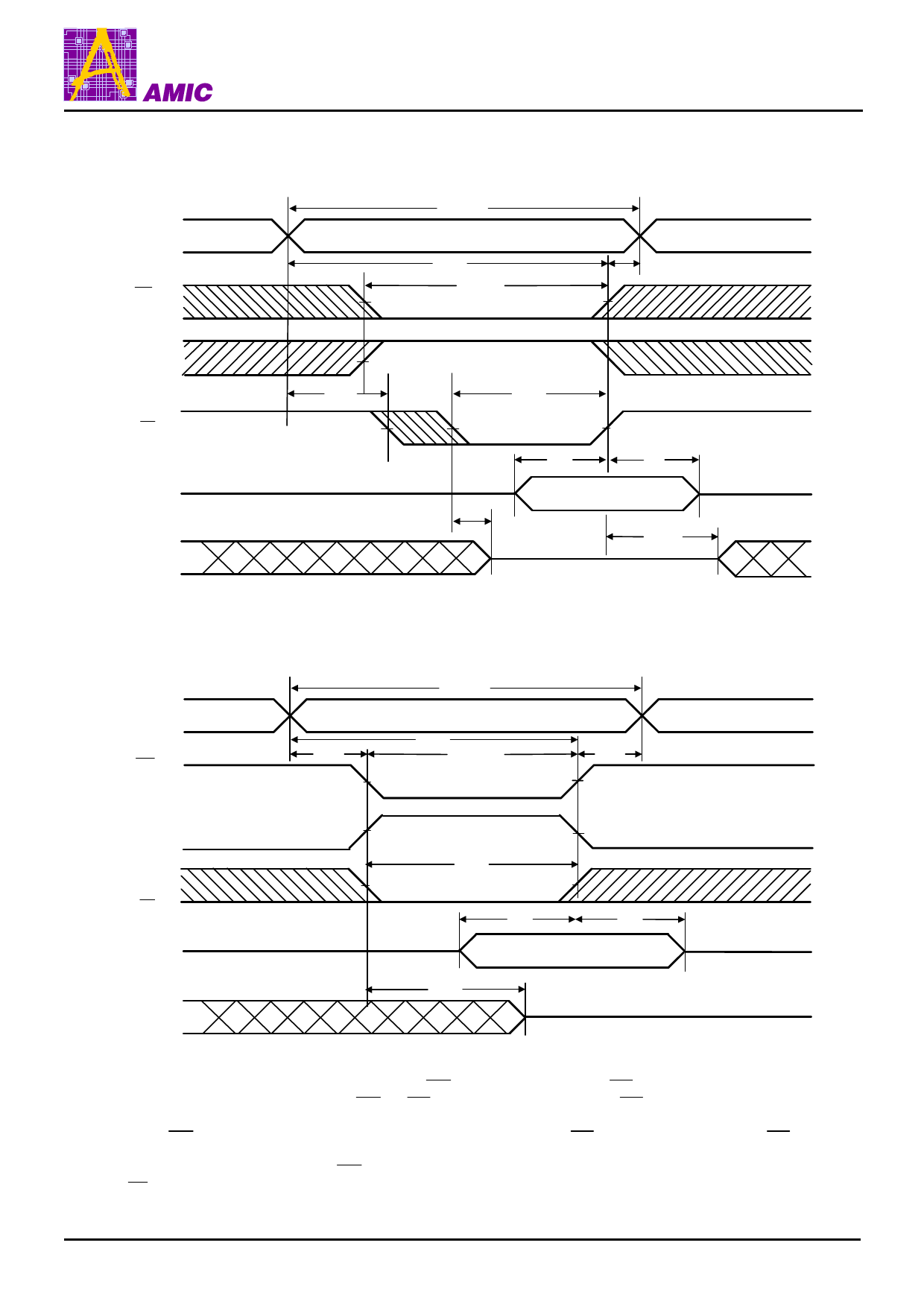

Timing Waveforms (continued)

Write Cycle 1(6)

(Write Enable Controlled)

Address

CE1

CE2

WE

(4)

tAS1

DIN

DOUT

LP62S4096E-T Series

tWC

tAW

tcw1 ,tcw2

tWR3

tWP2

tDW

tWHZ7

tDH

tOW7

Write Cycle 2(6)

(Chip Enable Controlled)

tWC

Address

CE1

tAS1

(4)

tAW

tCW1 , tCW2

tWR3

CE2

WE

tWP2

tDW

tDH

DIN

tWHZ7

DOUT

Notes: 1. tAS is measured from the address valid to the beginning of Write.

2. A Write occurs during the overlap (tWP) of a low CE1 or high CE2 , and a low WE .

3. tWR is measured from the earliest of CE1 or WE going high or CE2 going low WE going high to the end of the Write

cycle.

4. If the CE1 low or CE2 high transition occurs simultaneously with the WE low transition or after the WE transition,

outputs remain in a high impedance state.

5. tCW is measured from the later of CE1 going low or CE2 going high to the end of Write.

6. OE level is high or low.

7. Transition is measured ±500mV from steady state. This parameter is sampled and not 100% tested.

(May, 2010, Version 3.3)

6

AMIC Technology, Corp.