NT256D64S88AAG-6 查看數據表(PDF) - Unspecified

零件编号

产品描述 (功能)

生产厂家

NT256D64S88AAG-6 Datasheet PDF : 14 Pages

| |||

NT256D64S88AAG

256MB : 32M x 64

PC2700 Unbuffered DIMM

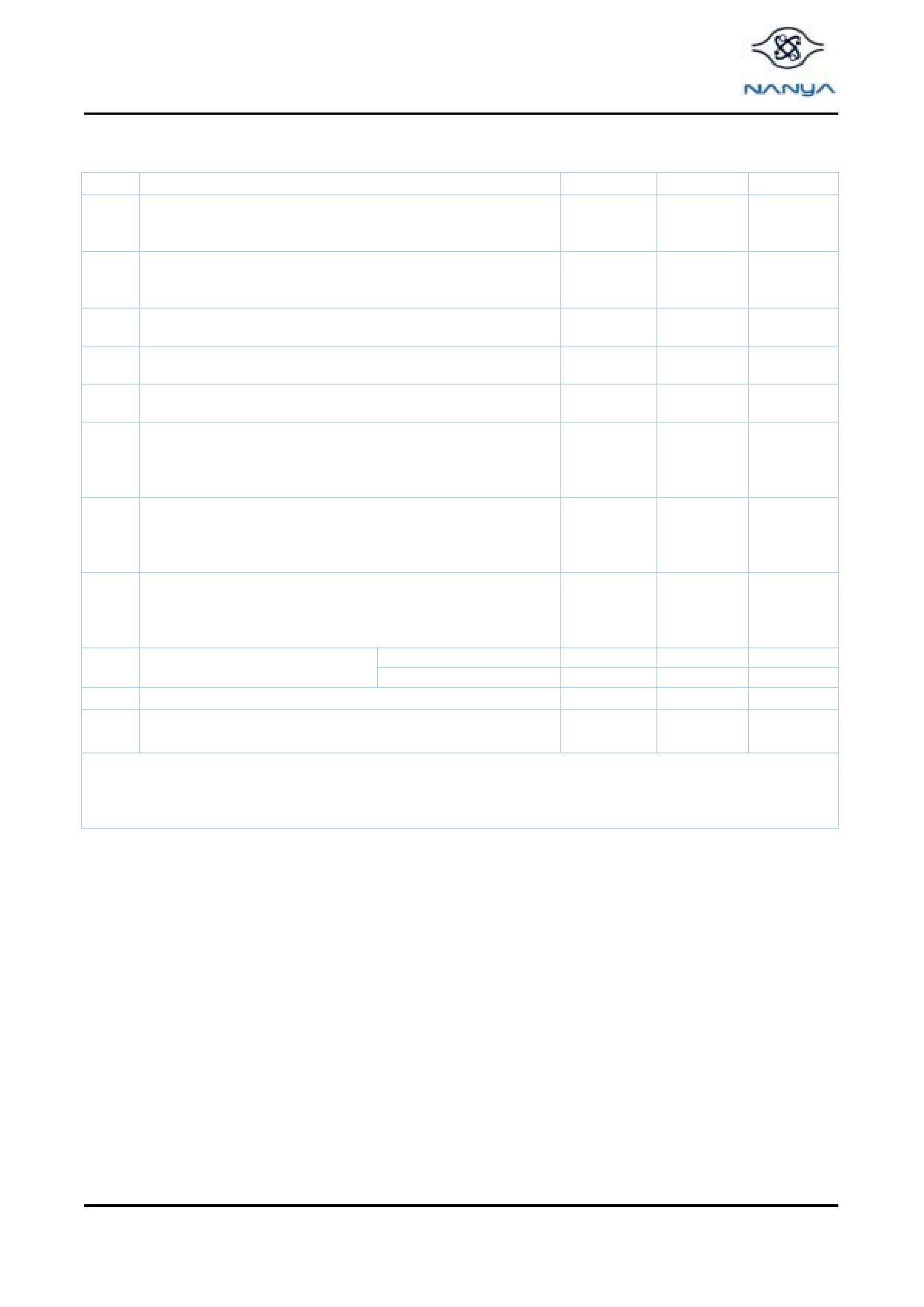

Operating, Standby, and Refresh Currents

(TA = 0 °C ~ 70 °C; VDDQ = 2.5V ± 0.2V; VDD = 2.5V ± 0.2V, See AC Characteristics)

Symbol

Parameter/Condition

PC2700

Unit

Operating Current : one bank; active / precharge; tRC = tRC (MIN) ;

I DD0 tCK = tCK (MIN) ; DQ, DM, and DQS inputs changing twice per clock cycle;

680

mA

address and control inputs changing once per clock cycle

Operating Current : one bank; active / read / precharge; Burst = 2;

I DD1

tRC = tRC (MIN) ; CL=2.5; tCK = tCK (MIN) ; IOUT = 0mA;

address and control inputs changing once per clock cycle

TBD

mA

I DD2P

Precharge Power-Down Standby Current :

all banks idle; power-down mode; CKE ≤ VIL (MAX) ; tCK = tCK (MIN)

200

mA

Idle Standby Current : CS ≥ VIH (MIN) ; all banks idle; CKE ≥ VIH(MIN) ;

I DD2N

tCK = tCK (MIN) ; address and control inputs changing once per clock cycle

280

mA

I DD3P

Active Power-Down Standby Current : one bank active;

power-down mode; CKE ≤ VIL (MAX) ; tCK = tCK (MIN)

200

mA

Active Standby Current : one bank; active / precharge; CS ≥ VIH (MIN) ;

CKE ≥ VIH (MIN) ; tRC = tRAS (MAX) ; tCK = tCK (MIN) ; DQ, DM, and DQS

I DD3N inputs changing twice per clock cycle;

480

mA

address and control inputs changing once per clock cycle

Operating Current : one bank; Burst = 2; reads; continuous burst;

I DD4R

address and control inputs changing once per clock cycle;

DQ and DQS outputs changing twice per clock cycle; CL = 2.5;

1320

mA

tCK = tCK (MIN) ; IOUT = 0mA

Operating Current : one bank; Burst = 2; writes; continuous burst;

I DD4W

address and control inputs changing once per clock cycle;

DQ and DQS inputs changing twice per clock cycle; CL=2.5;

1200

mA

tCK = tCK (MIN)

I DD5 Auto-Refresh Current :

t RC = t RFC (MIN)

t RC = 7.8 µs

1360

mA

132

mA

I DD6 Self-Refresh Current : CKE ≤ 0.2V

24

mA

Operating Current: four bank; four bank interleaving with BL = 4, address

I DD7 and control inputs randomly changing; 50% of data changing at every

TBD

mA

transfer; tRC = tRC (min); IOUT = 0mA.

1. I DD specifications are tested after the device is properly initialized.

2. Input slew rate = 1V/ ns.

3. Enables on-chip refresh and address counters.

4. Current at 7.8 µs is time averaged value of IDD5 at tRFC (MIN) and IDD2P over 7.8 µs.

Notes

1,2

1,2

1,2

1,2

1,2

1,2

1,2

1,2

1,2

1,2,4

1,2,3

1

REV 1.0 06 / 2002

10

© NANYA TECHNOLOGY CORP.

NANYA TECHNOLOGY CORP. reserves the right to change Products and Specifications without notice.