ISPLSI1016E-100LJ(1998) 查看數據表(PDF) - Lattice Semiconductor

零件编号

产品描述 (功能)

生产厂家

ISPLSI1016E-100LJ Datasheet PDF : 12 Pages

| |||

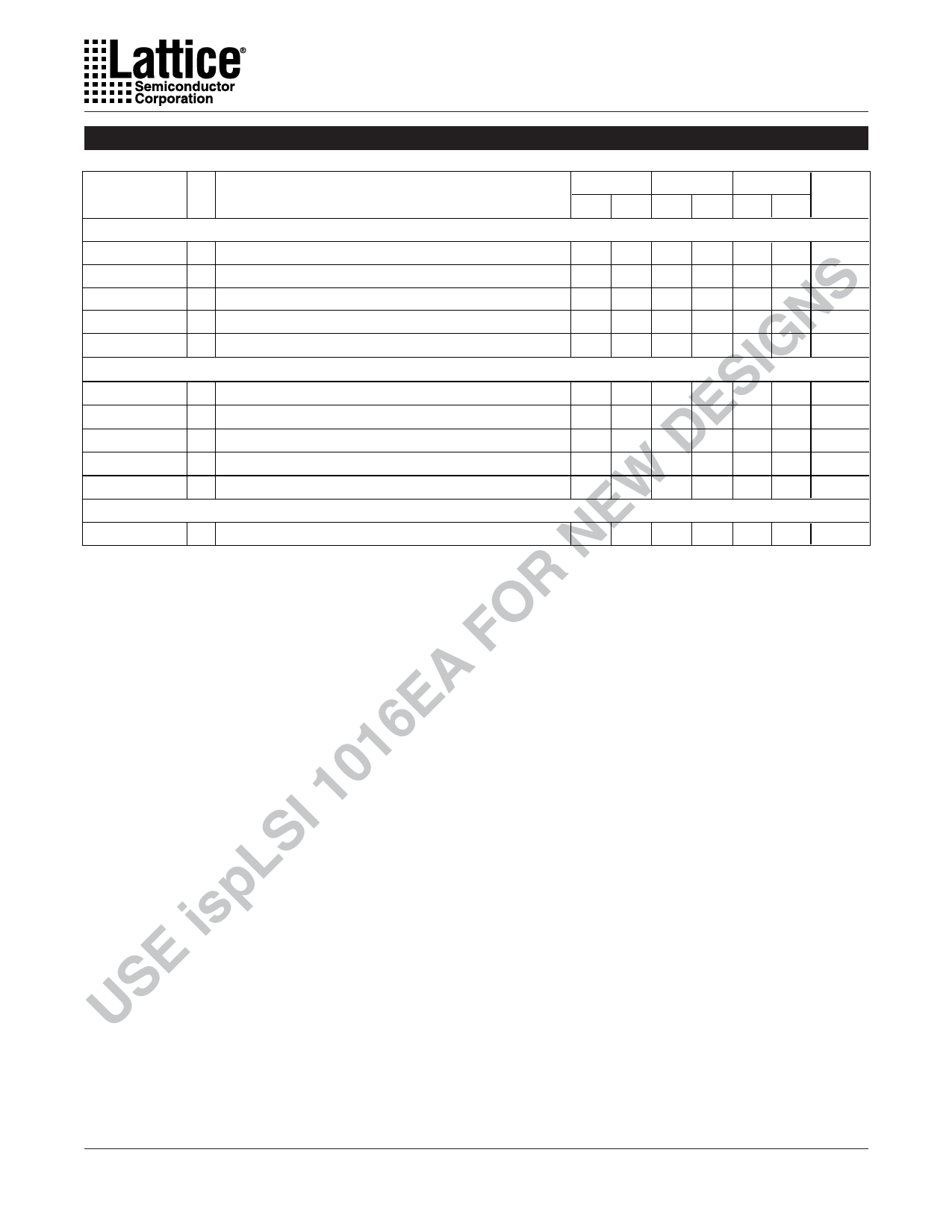

Specifications ispLSI 1016E

Internal Timing Parameters1

PARAMETER #2

DESCRIPTION

Outputs

tob

tsl

toen

49 Output Buffer Delay

50 Output Slew Limited Delay Adder

51 I/O Cell OE to Output Enabled

todis

52 I/O Cell OE to Output Disabled

tgoe

53 Global Output Enable

Clocks

tgy0

54 Clock Delay, Y0 to Global GLB Clock Line (Ref. clock)

tgy1/2

tgcp

tioy1/2

55 Clock Delay, Y1 or Y2 to Global GLB Clock Line

56 Clock Delay, Clock GLB to Global GLB Clock Line

57 Clock Delay, Y1 or Y2 to I/O Cell Global Clock Line

tiocp

58 Clock Delay, Clock GLB to I/O Cell Global Clock Line

Global Reset

tgr

59 Global Reset to GLB and I/O Registers

1. Internal Timing Parameters are not tested and are for reference only.

2. Refer to Timing Model in this data sheet for further details.

-125

-100

-80

UNITS

MIN. MAX. MIN. MAX. MIN. MAX.

– 1.4 – 1.7 – 3.0 ns

– 10.0 – 10.0 – 10.0 ns

– 4.3 – 5.3 – 6.4 ns

– 4.3 – 5.3 – 6.4 ns

– 2.7 – 3.7 – 4.1 ns

1.3 1.3 1.4 1.4 2.1 2.1 ns

2.3 2.7 2.4 2.9 3.6 4.4 ns

0.8 1.8 0.8 1.8 1.2 2.7 ns

0.0 0.3 0.0 0.4 0.0 0.6 ns

0.8 1.8 0.8 1.8 1.2 2.7 ns

– 3.2 – 4.5 – 5.5 ns

Table 2-0037-16/125,100,80

7