DS17887 查看數據表(PDF) - Maxim Integrated

零件编号

产品描述 (功能)

生产厂家

DS17887 Datasheet PDF : 31 Pages

| |||

DS17285/DS17287/

DS17485/DS17487/

DS17885/DS17887

Real-Time Clocks

Pin Description (continued)

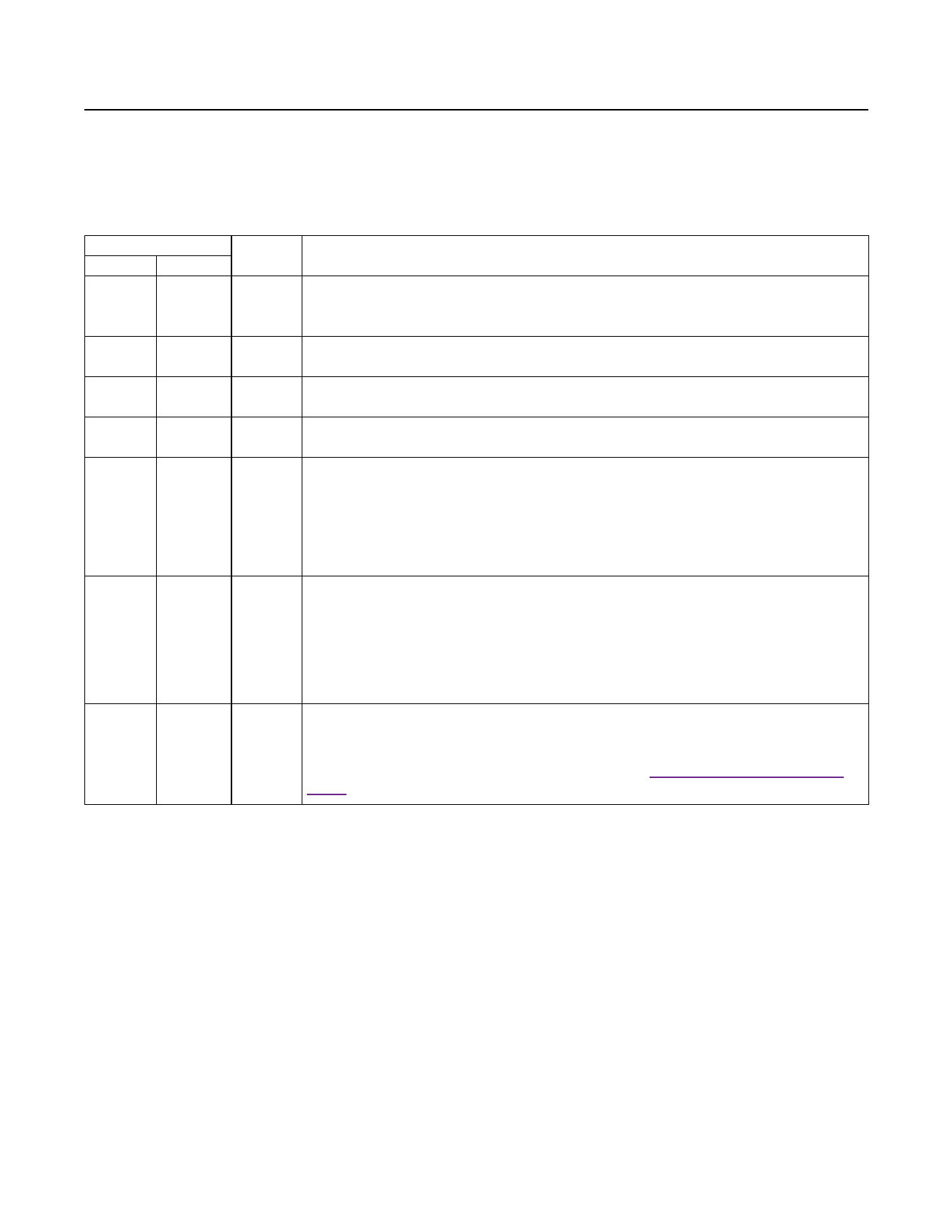

PIN

24

28

13

23

NAME

FUNCTION

Active-Low Chip-Select Input. This pin must be asserted low during a bus cycle for the device

CS to be accessed. CS must be kept in the active state during RD and WR. Bus cycles that take

place without asserting CS latch addresses, but no access occurs.

14

24

ALE

Address Latch Enable Input, Active High. This input pin is used to demultiplex the address/data

bus. The falling edge of ALE causes the address to be latched within the device.

15

25

WR

Active-Low Write Input. This pin defines the period during which data is written to the

addressed register.

17

27

RD

Active-Low Read Input. This pin identifies the period when the device drives the bus with read

data. It is an enable signal for the output buffers of the device.

Active-Low Kickstart Input. When VCC is removed from the device, the system can be powered

on in response to an active-low transition on the KS pin, as might be generated from a key

18

28

KS

closure. VBAUX must be present and auxiliary-battery-enable bit (ABE) must be set to 1 if the

kickstart function is used, and the KS pin must be pulled up to the VBAUX supply. While VCC

is applied, the KS pin can be used as an interrupt input. If not used, KS must be grounded and

ABE set to 0.

Active-Low Interrupt Request. This pin is an active-low output that can be used as an interrupt

input to a processor. The IRQ output remains low as long as the status bit causing the interrupt

is present and the corresponding interrupt-enable bit is set. To clear the IRQ pin, the application

19

1

IRQ software must clear all enabled flag bits contributing to the pin’s active state. When no interrupt

conditions are present, the IRQ level is in the high-impedance state. Multiple interrupting

devices can be connected to an IRQ bus, provided that they are all open drain. The IRQ pin

requires an external pullup resistor to VCC.

Connection for Primary Battery. This supply input is used to power the normal clock functions

when VCC is absent. Diodes placed in series between VBAT and the battery can prevent proper

20

2

VBAT operation. If VBAT is not required, the pin must be grounded. UL recognized to ensure against

reverse charging current when used with a lithium battery (www.maximintegrated.com/qa/

info/ul). This pin is missing (N.C.) on the EDIP package.

www.maximintegrated.com

Maxim Integrated │ 8