CLRC63201T 查看數據表(PDF) - NXP Semiconductors.

零件编号

产品描述 (功能)

生产厂家

CLRC63201T Datasheet PDF : 127 Pages

| |||

NXP Semiconductors

CLRC632

Standard multi-protocol reader solution

Table 6. SPI compatibility

CLRC632 pins

ALE

A2

A1

A0

NRD

NWR

NCS

D7 to D1

D0

SPI pins

NSS

SCK

LOW

MOSI

HIGH

HIGH

LOW

do not connect

MISO

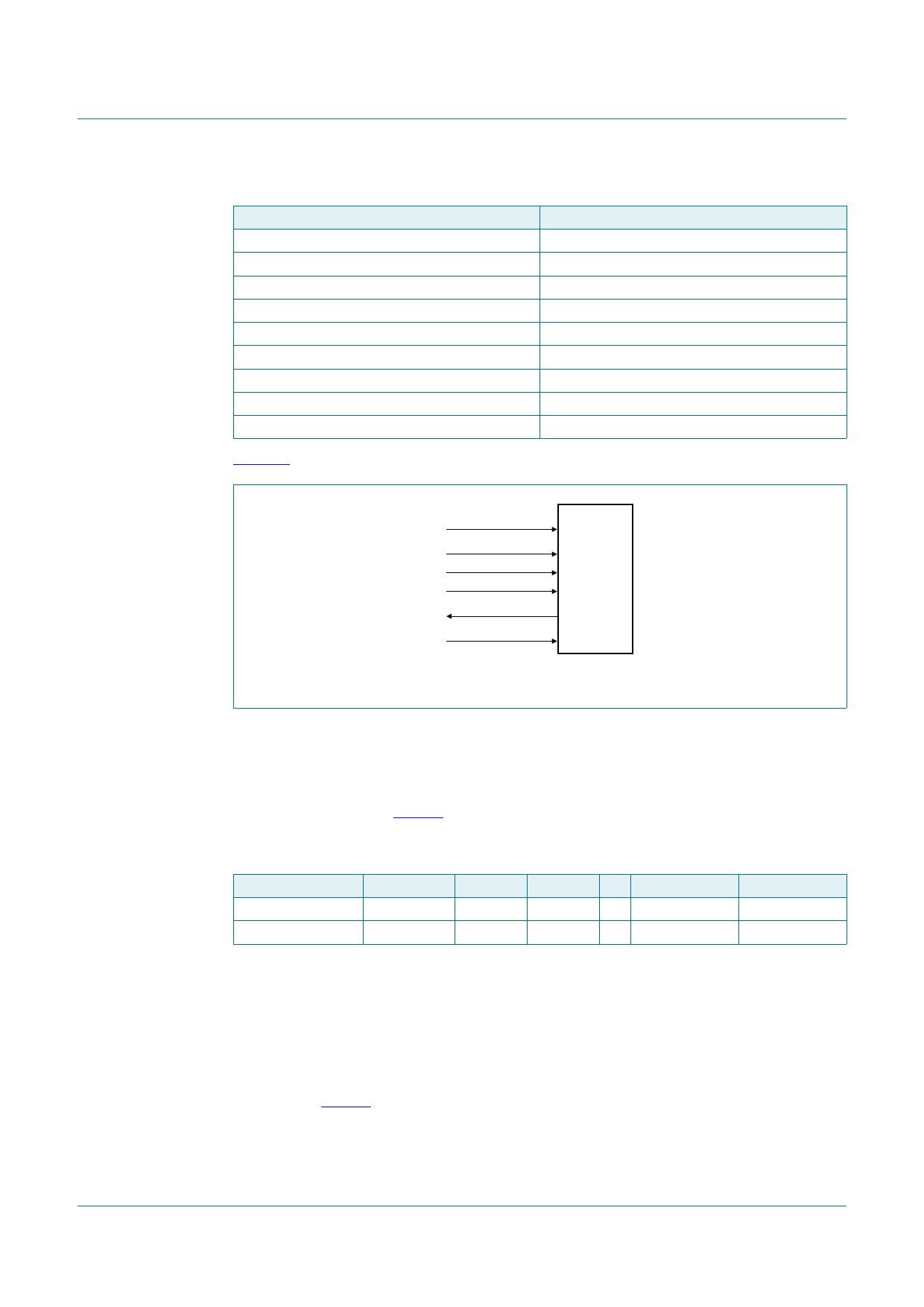

Figure 6 shows the microprocessor connection to the CLRC632 using SPI.

LOW

SCK

LOW

MOSI

MISO

NSS

DEVICE

NCS

A2

A1

A0

D0

ALE

001aak610

Fig 6. Connection to microprocessor: SPI

Remark: The SPI implementation for CLRC632 conforms to the SPI standard and

ensures that the CLRC632 can only be addressed as a slave.

9.1.4.1 SPI read data

The structure shown in Table 7 must be used to read data using SPI. It is possible to read

up to n-data bytes. The first byte sent defines both, the mode and the address.

Table 7.

Pin

MOSI

MISO

SPI read data

Byte 0

address 0

XX

Byte 1 Byte 2 ...

address 1 address 2 ...

data 0 data 1 ...

Byte n

address n

data n 1

Byte n + 1

00

data n

The address byte must meet the following criteria:

• the Most Significant Bit (MSB) of the first byte sets the mode. To read data from the

CLRC632 the MSB is set to logic 1

• bits [6:1] define the address

• the Least Significant Bit (LSB) should be set to logic 0.

As shown in Table 8, all the bits of the last byte sent are set to logic 0.

CLRC632

Product data sheet

COMPANY PUBLIC

All information provided in this document is subject to legal disclaimers.

Rev. 3.7 — 27 February 2014

073937

© NXP Semiconductors N.V. 2014. All rights reserved.

10 of 127