MAX697CWE 查看數據表(PDF) - Maxim Integrated

零件编号

产品描述 (功能)

生产厂家

MAX697CWE Datasheet PDF : 16 Pages

| |||

MAX696/MAX697

Microprocessor Supervisory Circuits

LLIN

1.312V

RESET

OUTPUT

50ms

LOW LINE

OUTPUT

1.3V

1.312V

1.3V

50ms

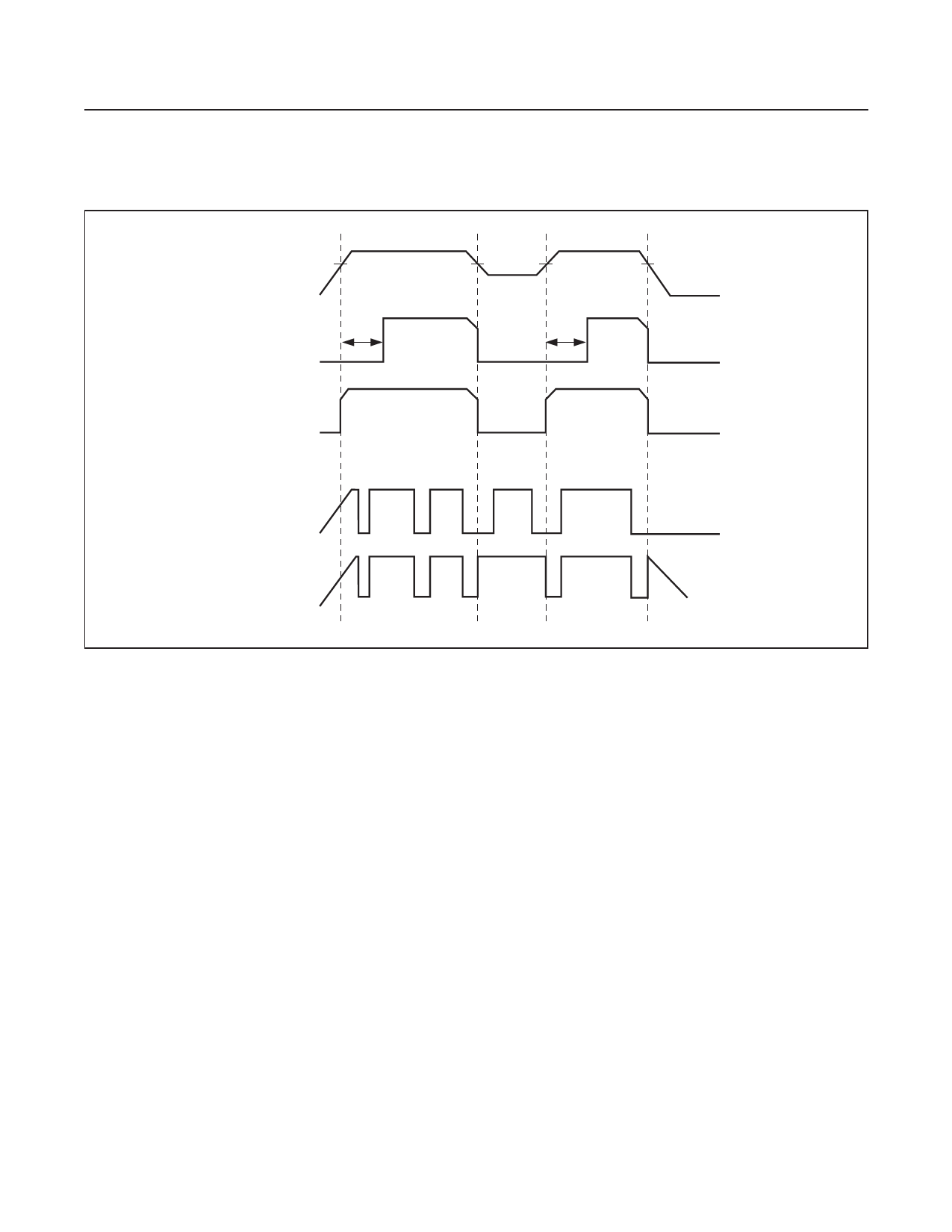

(MAX697) CE IN

(MAX697) CE OUT

Figure 5. MAX697 Reset Timing

CE Gating and RAM Write Protection

The MAX697 uses two pins to control the CE or WRITE

inputs of CMOS RAMs. When LLIN is > 1.3V, CE OUT is a

buffered replica of CE IN, with a 50ns propagation delay.

If LLIN input falls below 1.3V (1.2V min, 1.4V max), an

internal gate forces CE OUT high, independent of CE IN.

The CE output is also forced high when VCC is less than

VBATT. (See Figure 4.)

CE OUT typically drives the CE, CS, or WRITE input of

battery backed up CMOS RAM. This ensures the integrity

of the data in memory by preventing write operations when

VCC is at an invalid level. Similar protection of EEPROMs

can be achieved by using the CE OUT to drive the STORE

or WRITE inputs of an EEPROM, EAROM, or NOVRAM.

If the 50ns typical propagation delay of CE OUT is too

long, connect CE IN to GND and use the resulting CE

OUT to control a high-speed external logic gate. A second

alternative is to AND the LOW LINE output with the CE or

WR signal. An external logic gate and the RESET output

of the MAX696/MAX697 can also be used for CMOS RAM

write protection.

1.25V Comparator and Power-Fail Warning

The power-fail input (PFI) is compared to an internal 1.3V

reference. The power-fail output (PFO) goes low when the

voltage at PFI is less than 1.3V. Typically PFI is driven bay

an external voltage-divider that senses either the unregu-

lated DC input to the system’s VCC regulator or the regu-

lated output. The voltage-divider ration can be chosen so

the voltage at PFI falls below 1.3V several milliseconds

before the LLIN falls below 1.3V. PFO is normally used to

interrupt the microprocessor so that data can be stored in

RAM before LLIN falls below 1.3V and the RESET output

goes low.

The power-fail detector can also monitor the backup bat-

tery to warn of a low-battery condition. To conserve bat-

tery power, the power-fail detector comparator is turned

off and PFO is forced low when VCC is lower than the

VBATT input voltage.

Watchdog Timer and Oscillator

The watchdog circuit monitors the activity of the micropro-

cessor. If the microprocessor does not toggle the watch-

dog input (WDI) within the selected timeout period, a 50ms

RESET pulse is generated. Since many systems cannot

service the watchdog timer immediately after a reset,

the MAX696/MAX697 have a longer timeout period after

www.maximintegrated.com

Maxim Integrated │ 10