MAX197 وں¥çœ‹و•¸و“ڑè،¨ï¼ˆPDF) - Maxim Integrated

零ن»¶ç¼–هڈ·

ن؛§ه“پوڈڈè؟° (هٹں能)

ç”ںن؛§هژ‚ه®¶

MAX197

MAX197 Datasheet PDF : 16 Pages

| |||

Multi-Range (آ±10V, آ±5V, +10V, +5V),

Single +5V, 12-Bit DAS with 8+4 Bus Interface

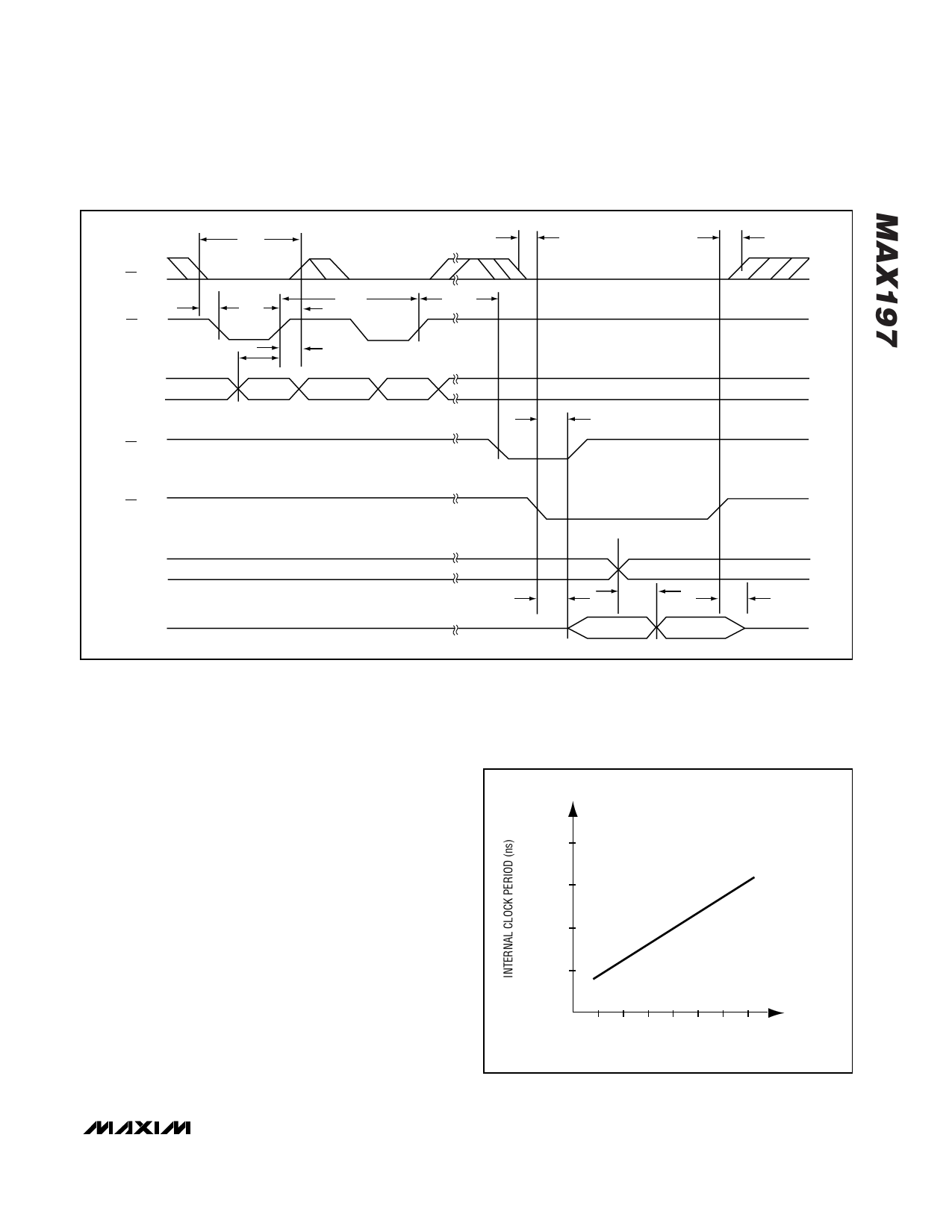

tCS

CS

tCSWS

WR

D7–D0

tWR

tDS

CONTROL

BYTE

ACQMOD = "1"

tCSHtAWCQI

tCONV

tDH

CONTROL

BYTE

ACQMOD = "0"

INT

RD

tCSRS

tINT1

tCSRH

HBEN

tD0

DOUT

Figure 6. Conversion Timing Using External Acquisition Mode

tD01

tTR

HIGH / LOW

BYTE VALID

HIGH / LOW

BYTE VALID

How to Read a Conversion

A standard interrupt signal, INT, is provided to allow the

device to flag the آµP when the conversion has ended

and a valid result is available. INT goes low when con-

version is complete and the output data is ready

(Figures 5 and 6). It returns high on the first read cycle

or if a new control byte is written.

Clock Modes

The MAX197 operates with either an internal or an

external clock. Control bits (D6, D7) select either inter-

nal or external clock mode. Once the desired clock

mode is selected, changing these bits to program

power-down will not affect the clock mode. In each

mode, internal or external acquisition can be used. At

power-up, external clock mode is selected.

Internal Clock Mode

Select internal clock mode to free the آµP from the

burden of running the SAR conversion clock. To select

this mode, write the control byte with D7 = 0 and D6 = 1.

A 100pF capacitor between the CLK pin and ground

sets this frequency to 1.56MHz nominal. Figure 7

shows a linear relationship between the internal clock

period and the value of the external capacitor used.

2000

1500

1000

500

0

0 50 100 150 200 250 300 350

CLOCK PIN CAPACITANCE (pF)

Figure 7. Internal Clock Period vs. Clock Pin Capacitance

______________________________________________________________________________________ 11