Q-67107-H5236 查看數據表(PDF) - Micronas

零件编号

产品描述 (功能)

生产厂家

Q-67107-H5236 Datasheet PDF : 154 Pages

| |||

SDA 9402/02S(A31)

Preliminary Data Sheet 02.2001

System Description

5.1.4 Synchronization

After elimination of the high frequency components of the CVBS signal by a low pass

filter, horizontal and vertical sync pulses are separated. Horizontal sync pulses are

generated by a digital phase locked loop. The time constant can be adjusted between

fast and slow behavior in four steps (PLLTC) to accommodate different input sources

(e.g. VCR). The time-constant can be changed during normal operation without visible

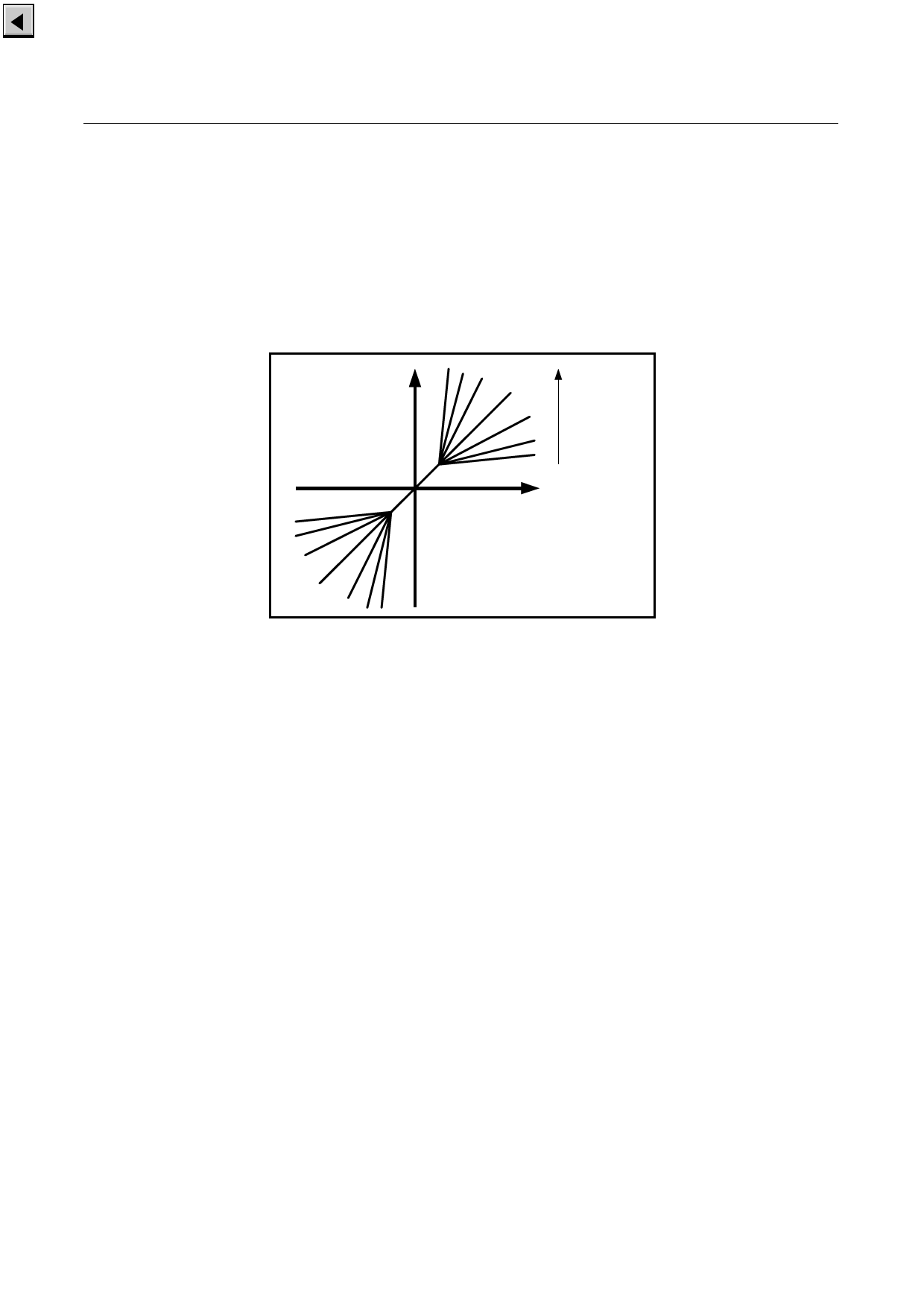

picture degradation. A fine tuning of the PLL time constant can be done by NSRED.

multiplication

before PLL

NSRED

(I²C)

phase deviation

Figure 5-5 NSRED characteristic

Additionally weak input signals from a satellite dish (’fish’) become more stable when

SATNR is enabled. Vertical sync pulses are separated by integration of equalizing

pulses. A vertical flywheel mode improves vertical sync separation for weak signals

(VFLYWHL, VFLYWHLMD). Additionally, v-syncs may be gated by VTHRL and VTHRH

to reject invalid v-syncs. When no input signal is connected the device switches to a free-

running mode. The device can be configured to switch-on background color when no or

only a weak signal is applied (NOSIGB). 50 Hz or 60 Hz operation for sync separation

may be forced separately or selected to work automatically (FLNSTRD)

Micronas

5-20