DM560P 查看數據表(PDF) - Davicom Semiconductor, Inc.

零件编号

产品描述 (功能)

生产厂家

DM560P Datasheet PDF : 43 Pages

| |||

DM560P

V.90 Integrated Data/Fax/Voice/Speakerphone Modem Device Set

1: In _ buffer empty (clear automatically by a

write to In _buffer)

0: In _ buffer not empty

Bit7: reset bit(write only)

1: software reset

(4)CRCL register: Address DC0AH (read only)

(5)CRCH register: Address DC0BH (read only)

UART (16550A) Emulation Registers

Receiver Buffer (Read), Transmitter Holding

Register (Write): Address: 0 (DLAB=0)

Reset State 00h

bit7 bit6 bit5 bit4 bit3 Bit2 bit1 bit0

dat7 dat6 dat5 dat4 dat3 Dat2 dat1 dat0

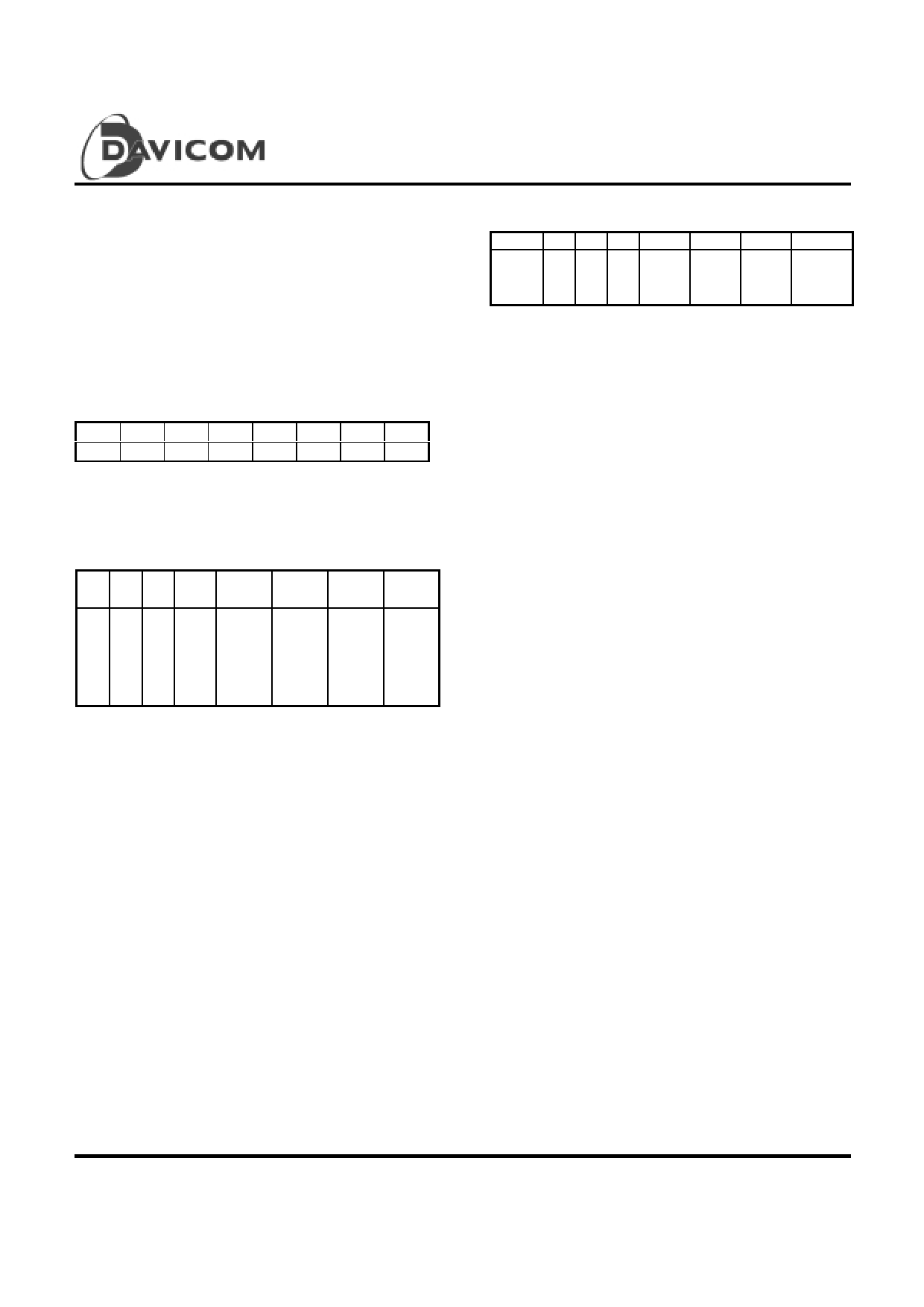

Interrupt Identification Register (IIR): Address 2

Reset State 01h, Read only

Bit7 Bit6 bit5 bit4 bit3 bit2 bit1 bit0

FIFO 0 0 0 D3: D2: D1: D0:

Enable

INTD2 INTD1 INTD0 int

Pending

In order to provide minimum software overhead

during data transfers, the virtual UART prioritizes

interrupts into four levels as follows: Receiver Line

Status (priority 1), Receiver Data Available (priority

2), Character Timeout Indication (priority 2, FIFO

mode only), Transmitter Holding Register Empty

(priority 3), and Modem Status (priority 4).

When this register address is read, it contains the

parallel received data. Data to be transmitted is

written to this register.

Interrupt Enable Register (IER): Address 1

The IIR register gives prioritized information

regarding the status of interrupt conditions. When

accessed, the IIR indicates the highest priority

interrupt that is pending.

Reset State 00h, Write Only

bit7 bit6 bit Bit4 bit3 bit2 bit1 bit0

5

000

0 Enable Enable Enable Enable

Modem Line

TX

RX

Status Status Holding Data

Intr Intr Registe Intr

r

Intr

Bit 0: This bit can be used in either a prioritized

interrupt or polled environment to indicate

whether an interrupt is pending. When this bit

is a logic 0, an interrupt is pending, and the IIR

contents may be used as a pointer to the

appropriate interrupt service routine. When bit

0 is a logic 1, no interrupt is pending, and

polling (if used) continues.

This 8-bit register enables the four types of interrupts

as described below. Each interrupt source can

activate the INT output signal if enabled by this

register. Resetting bits 0 through 3 will disable all

UART interrupts.

Bit 0: This bit enables the Received Data Available

and timeout interrupts in the FIFO mode when

set to logic 1.

Bit 1-2: These two bits of the IIR are used to identify

the highest priority interrupt pending, as

indicated in the table below.

Bit 3: In character mode, this bit is 0. In FIFO mode,

this bit is set, along with bit 2, when a timeout

interrupt is pending.

Bit 4-6: Not used

Bit 1: This bit enables the Transmitter Holding

Register Empty Interrupt when set to logic 1.

Bit 7: FIFO always enabled.

Bit 2: This bit enables the Receiver Line Status

Interrupt when set to logic 1.

Bit 3: This bit enables the MODEM Status Interrupt

when set to logic 1.

Bit 4-7: Not used

Preliminary

11

Version: DM560P-DS-P07

August 11, 2000