CDB5333 查看數據表(PDF) - Cirrus Logic

零件编号

产品描述 (功能)

生产厂家

CDB5333 Datasheet PDF : 20 Pages

| |||

3. PIN DESCRIPTION

Interface Power

Master Clock

Serial Clock

Serial Data Output

Analog Power

Ground

Left Right Clock

MCLK Divide

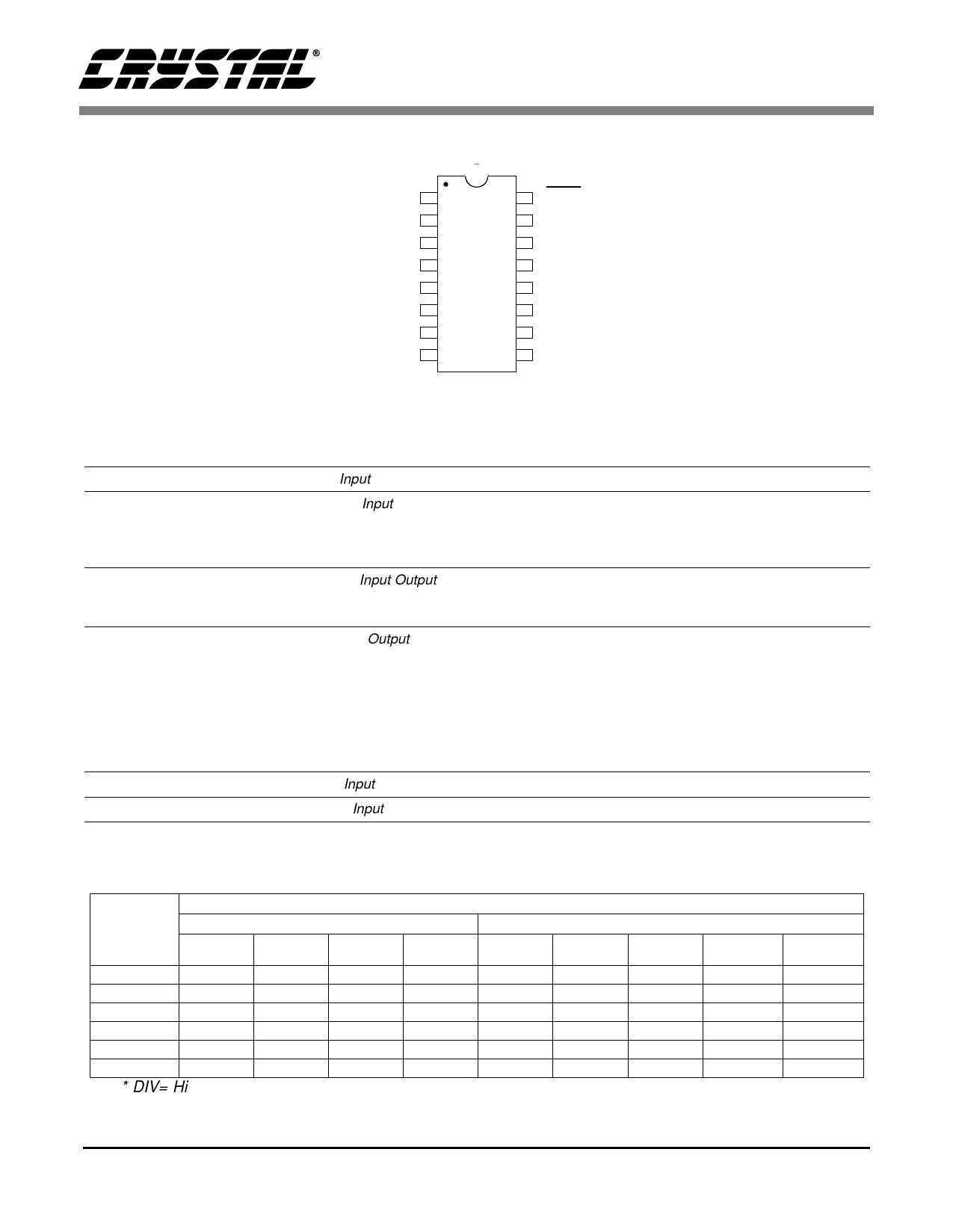

CS5333

VL 1 16 RST

Reset

MCLK 2 15 VQ

Quiescent Voltage

SCLK 3 14 AINL

Left Channel Analog Input

SDATA 4 13 AINR Right Channel Analog Input

VA 5 12 REF_GND Reference Ground

GND 6 11 FILT+ Positive Voltage Reference

LRCK 7 10 TST

Test Input

DIV 8

9 DIF

Digital Interface Format

Interface Power

Master Clock

Serial Clock

Serial Audio Data

Out (M/S select)

Analog Power

Ground

1

VL (Input) - Digital interface power supply. Typically 1.8 to 3.3 VDC.

2

MCLK (Input) - The master clock frequency must be either 256x, 384x, 512x, 768x or

1024x the input sample rate in Base Rate Mode (BRM) and 128x, 192x, 256x, 384x the

input sample rate in High Rate Mode (HRM). Table 1 illustrates several standard audio

sample rates and the required master clock frequencies.

3

SCLK (Input/Output) - Clocks the individual bits of the serial data out of the SDOUT pin.

The required relationship between the Left/Right clock, serial clock and serial data is

defined by the DIF pin.

4

SDATA (Output) - This pin serves two functions.

First: two’s complement MSB-first serial data is output on this pin. The data is clocked out

of SDOUT via the serial clock and the channel is determined by the Left/Right clock. The

required relationship between the Left/Right clock, serial clock and serial data is defined

by the DIF pin.

Second: Master/Slave mode selection is determined, at startup, by a 47 kOhm pullup/pull-

down on this line. A pullup to VL selects Master mode and a pulldown to GND selects

Slave mode.

5

VA (Input) - Analog power supply. Typically 1.8 to 3.3 VDC.

6

GND (Input) - Ground Reference.

Sample

Rate

(kHz)

128x

32

4.0960

44.1

5.6448

48

6.1440

64

8.1920

88.2

11.2896

96

12.2880

* DIV= Hi

HRM

192x

256x*

6.1440

8.4672

9.2160

12.2880

16.9344

18.4320

8.1920

11.2896

12.2880

16.3840

22.5792

24.5760

MCLK (MHz)

384x*

12.2880

16.9344

18.4320

24.5760

33.8688

36.8640

256x

8.1920

11.2896

12.2880

-

-

-

384x

12.2880

16.9344

18.4320

-

-

-

Table 1. Common Clock Frequencies

BRM

512x

16.3840

22.5792

24.5760

-

-

-

768x*

24.5760

32.7680

36.8640

-

-

-

1024x*

32.7680

45.1584

49.1520

-

-

-

DS520PP1

11