1417H5 وں¥çœ‹و•¸و“ڑè،¨ï¼ˆPDF) - Agere -> LSI Corporation

零ن»¶ç¼–هڈ·

ن؛§ه“پوڈڈè؟° (هٹں能)

ç”ںن؛§هژ‚ه®¶

1417H5

1417H5 Datasheet PDF : 12 Pages

| |||

NetLight 1417G5 and 1417H5-Type

ATM/SONET/SDH Transceivers with Clock Recovery

Data Sheet

January 2000

Application Information (continued)

Noise that couples into the receiver through the power

supply pins can also degrade performance. It is recom-

mended that the pi filter, shown in Figure 2, be used for

both the transmitter and receiver power supplies.

Data Clock and Signal Detect Outputs

The data clock and signal detect outputs of the 1417

transceiver are driven by open-emitter NPN transistors,

which have an output impedance of approximately 7 Ω.

Each output can provide approximately 50 mA maxi-

mum current to a 50 Ω load terminated to VCC – 2.0 V.

Due to the high switching speeds of ECL outputs,

transmission line design must be used to interconnect

components. To ensure optimum signal fidelity, both

data outputs (RD+/RD–) and clock outputs (CLK+/

CLK–) should be terminated identically. The signal

lines connecting the data and clock outputs to the next

device should be equal in length and have matched

impedances. Controlled impedance stripline or micros-

trip construction must be used to preserve the quality

of the signal into the next component and to minimize

reflections back into the receiver, which could degrade

its performance. Excessive ringing due to reflections

caused by improperly terminated signal lines makes it

difficult for the component receiving these signals to

decipher the proper logic levels and can cause transi-

tions to occur where none were intended. Also, by min-

imizing high-frequency ringing, possible EMI problems

can be avoided.

The signal-detect output is LVTTL logic. A logic low at

this output indicates that the optical signal into the

receiver has been interrupted or that the light level has

fallen below the minimum signal detect threshold. This

output should not be used as an error rate indicator,

since its switching threshold is determined only by the

magnitude of the incoming optical signal.

Transceiver Processing

When the process plug is placed in the transceiver's

optical port, the transceiver and plug can withstand

normal wave soldering and aqueous spray cleaning

processes. However, the transceiver is not hermetic,

and should not be subjected to immersion in cleaning

solvents. The transceiver case should not be exposed

to temperatures in excess of 125 آ°C. The transceiver

pins can be wave soldered at 250 آ°C for up to 10 sec-

onds. The process plug should only be used once.

After removing the process plug from the transceiver, it

must not be used again as a process plug; however, if it

has not been contaminated, it can be reused as a dust

cover.

Transceiver Optical and Electrical Characteristics

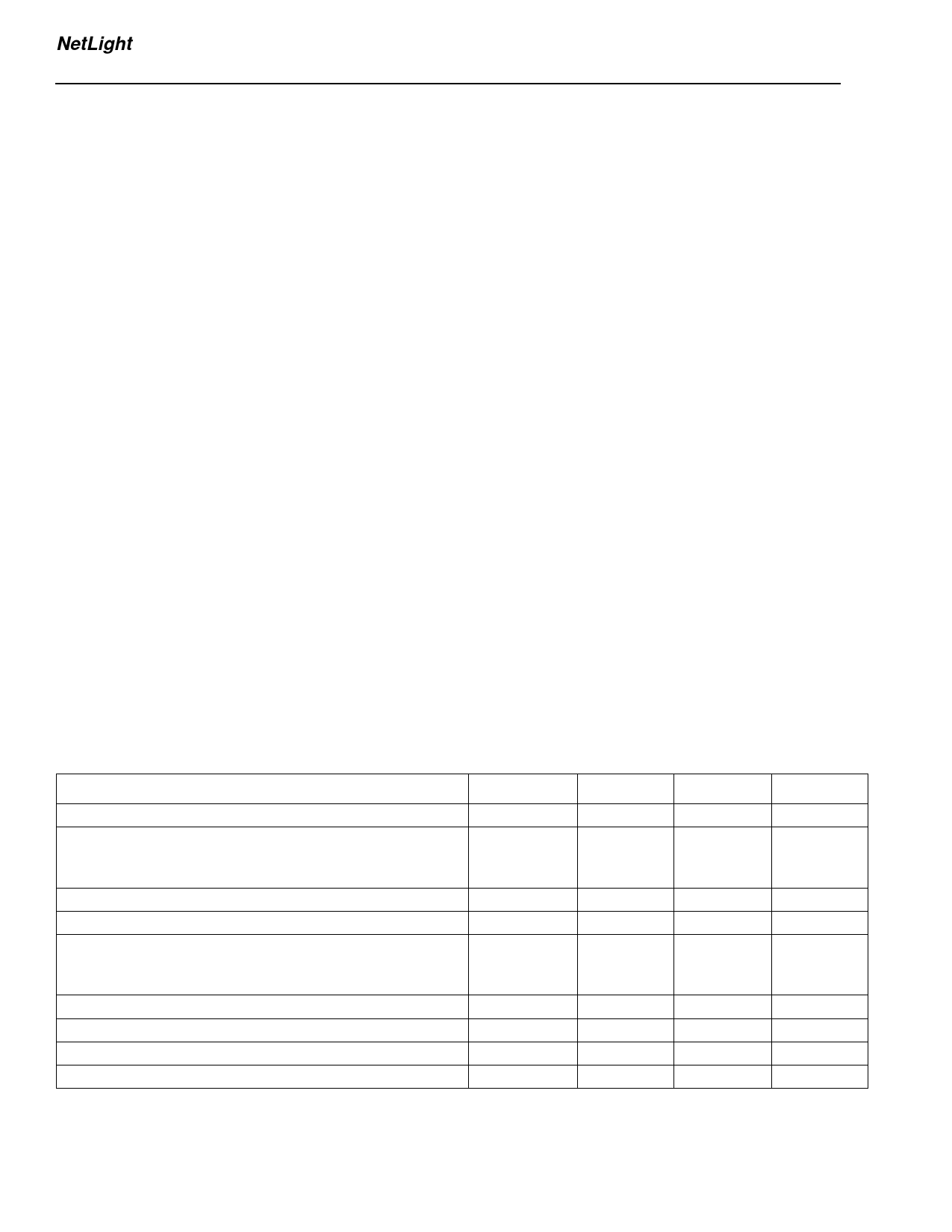

Table 2. Transmitter Optical and Electrical Characteristics (TC = –40 آ°C to +85 آ°C; VCC = 3.135 V to 3.465 V)

Parameter

Average Optical Output Power (EOL)

Optical Wavelength:

STM-1 (4 nm spectral width, maximum)

STM-4 (2.5 nm spectral width, maximum)

Dynamic Extinction Ratio

Power Supply Current

Input Data Voltage:

Low

High

Transmit Disable Voltage

Transmit Enable Voltage

Laser Bias Voltage

Laser Back-facet Monitor Voltage

Symbol

PO

خ»C

EXT

ICCT

Min

–15.0

1261

1274

8.2

—

Max

–8.0

1360

1356

—

150

VIL

VIH

VD

VEN

VBIAS

VBF

VCC – 1.81

VCC – 1.025

VCC – 1.3

VEE

0

0.01

VCC – 1.62

VCC – 0.88

VCC

VEE + 0.8

0.70

0.20

Unit

dBm

nm

nm

dB

mA

V

V

V

V

V

V

4

Agere Systems Inc.