HDD16M72D9W 查看數據表(PDF) - Hanbit Electronics Co.,Ltd

零件编号

产品描述 (功能)

生产厂家

HDD16M72D9W

HDD16M72D9W Datasheet PDF : 11 Pages

| |||

HANBit

HDD16M72D9W

Notes :

1. Maximum burst refresh cycle : 8

2. The specific requirement is that DQS be valid(High or Low) on or before this CK edge. The case shown(DQS going from High_Z

to logic Low) applies when no writes were previously in progress on the bus. If a pre vious write was in progress, DQS could be

High at this time, depending on tDQSS.

3. The maximum limit for this parameter is not a device limit. The device will operate with a great value for this parameter, but

system performance (bus turnaround) will degrade accordingly.

4. A write command can be applied with tRCD satisfied after this command.

5. For registered DIMMs, tCL and tCH are ≥ 45% of the period including both the half period jitter ( tJIT(HP) ) of the PLL and the half

jitter due to crosstalk (tJIT(crosstalk) ) on the DIMM.

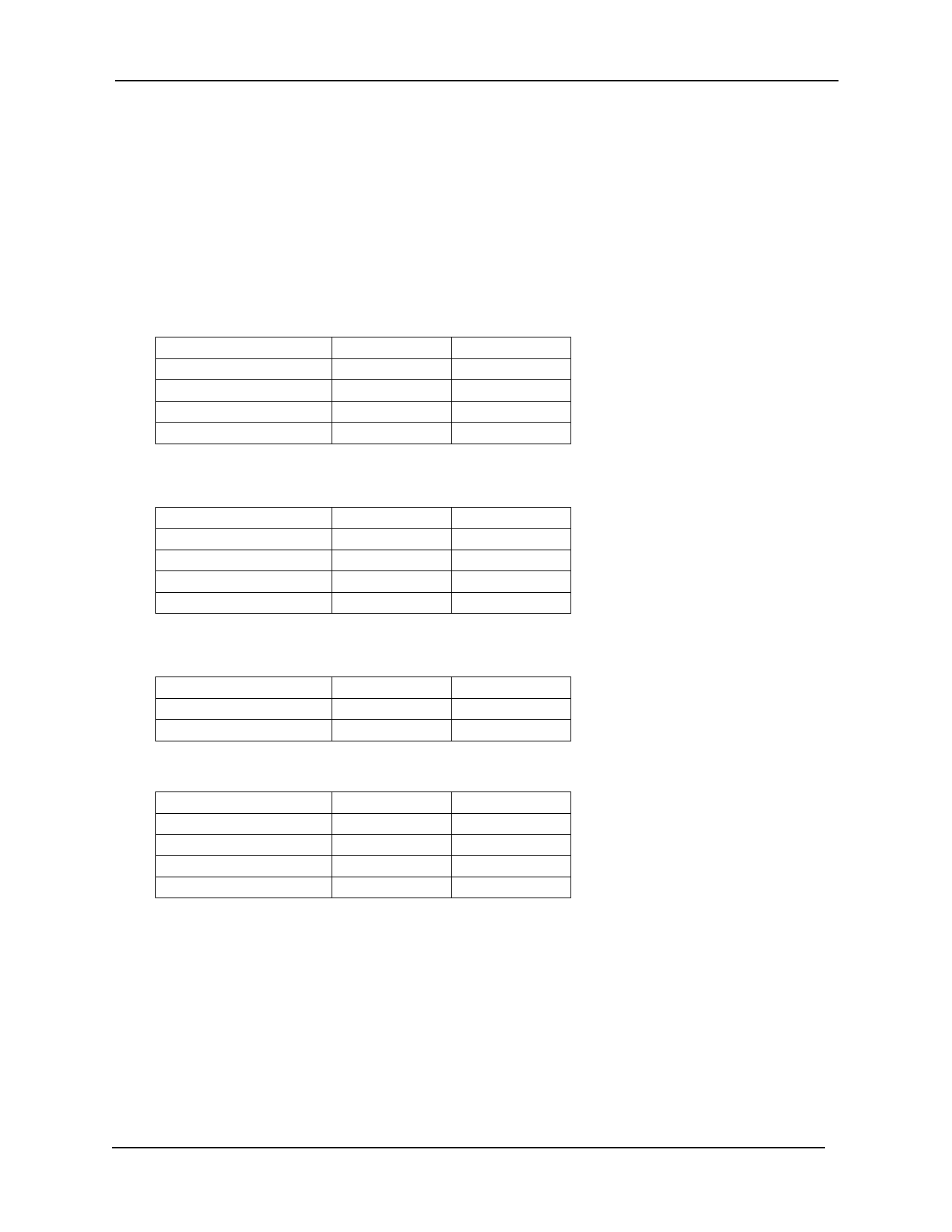

6. Input Setup/Hold Slew Rate Derating

Input Setup/Hold Slew Rate

Δ tIS

Δ tIH

(V/ns)

(ps)

(ps)

0.5

0

0

0.4

+50

+50

0.3

+100

+100

- This derating table is used to increase tDS/tDH in the case where the input slew rate is below 0.5V/ns. Input setup/hold slew rate

based on the lesser of AC-AC slew rate and DC-DC slew rate.

7. I/O Setup/Hold Slew Rate Derating

Input Setup/Hold Slew Rate

Δ tIS

Δ tIH

(V/ns)

(ps)

(ps)

0.5

0

0

0.4

+75

+75

0.3

+150

+150

- This derating table is used to increase tDS/tDH in the case where the I/O slew rate is below 0.5V/ns. I/O setup/hold slew rate based

on the lesser of AC-AC slew rate and DC-DC slew rate.

8. I/O Setup/Hold Plateau Derating

I/O Input Level

Δ tDS

Δ tDH

(mV)

(ps)

(ps)

± 280

+50

+50

- This derating table is used to increase tDS/tDH in the case where the input level is flat below VREF ± 310mV for a duration of up to 2ns.

9. I/O Delta Rise/Fall Rate(1/slew-rate) Derating

Delta Rise/Fall Rate

Δ tDS

Δ tDH

(ns/V)

(ps)

(ps)

0

0

0

±0.25

+50

+50

±0.5

+100

+100

- This derating table is used to increase tDS/tDH in the case where the DQ and DQS slew rates differ. The Delta Rise/Fall Rate is

calated as 1/SlewRate1-1/SlewRate2. For example, if slew rate 1 = 5V/ns and slew rate 2 =.4V/ns then the Delta Rise/Fall Rate =-

0/5ns/V. Input S/H slew rate based on larger of AC -AC delta rise/fall rate and DC-DC delta rise/fall rate.

10. This parameter is fir system simulation purpose. It is guranteed by design.

11. For each of the terms, if not already an integer, round to the next highest integer. t CK is actual to the system clock cycle time.

URL : www.hbe.co.kr

REV 1.0 (November.2002)

8

HANBit Electronics Co.,Ltd.