MCP23017 查看數據表(PDF) - Microchip Technology

零件编号

产品描述 (功能)

生产厂家

MCP23017 Datasheet PDF : 42 Pages

| |||

MCP23017/MCP23S17

2.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 2-1.

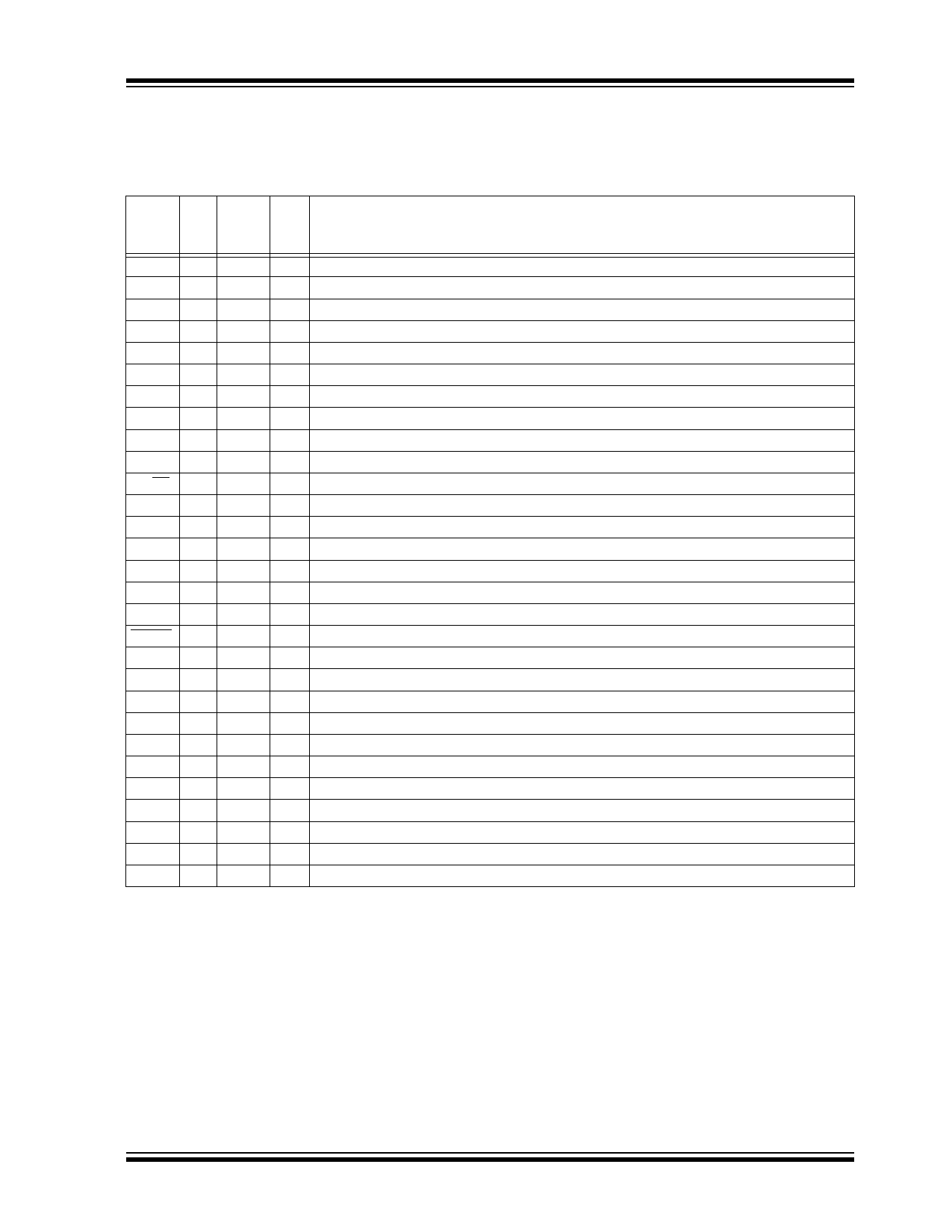

TABLE 2-1: PINOUT DESCRIPTION

Pin

Name

QFN

SOIC

SPDIP

SSOP

Pin

Type

Function

GPB0 25

1

I/O Bidirectional I/O pin. Can be enabled for interrupt-on-change and/or internal weak pull-up resistor.

GPB1 26

2

I/O Bidirectional I/O pin. Can be enabled for interrupt-on-change and/or internal weak pull-up resistor.

GPB2 27

3

I/O Bidirectional I/O pin. Can be enabled for interrupt-on-change and/or internal weak pull-up resistor.

GPB3 28

4

I/O Bidirectional I/O pin. Can be enabled for interrupt-on-change and/or internal weak pull-up resistor.

GPB4 1

5

I/O Bidirectional I/O pin. Can be enabled for interrupt-on-change and/or internal weak pull-up resistor.

GPB5 2

6

I/O Bidirectional I/O pin. Can be enabled for interrupt-on-change and/or internal weak pull-up resistor.

GPB6 3

7

I/O Bidirectional I/O pin. Can be enabled for interrupt-on-change and/or internal weak pull-up resistor.

GPB7 4

8

I/O Bidirectional I/O pin. Can be enabled for interrupt-on-change and/or internal weak pull-up resistor.

VDD

5

9

P Power

VSS

6

10

P Ground

NC/CS 7

11

I NC (MCP23017)/Chip Select (MCP23S17)

SCK

8

12

I Serial clock input

SDA/SI 9

13 I/O Serial data I/O (MCP23017)/Serial data input (MCP23S17)

NC/SO 10 14

O NC (MCP23017)/Serial data out (MCP23S17)

A0

11

15

I Hardware address pin. Must be externally biased.

A1

12 16

I Hardware address pin. Must be externally biased.

A2

13 17

I Hardware address pin. Must be externally biased.

RESET 14 18

I Hardware reset. Must be externally biased.

INTB

15 19

O Interrupt output for PORTB. Can be configured as active-high, active-low or open-drain.

INTA

16 20

O Interrupt output for PORTA. Can be configured as active-high, active-low or open-drain.

GPA0 17 21 I/O Bidirectional I/O pin. Can be enabled for interrupt-on-change and/or internal weak pull-up resistor.

GPA1 18 22 I/O Bidirectional I/O pin. Can be enabled for interrupt-on-change and/or internal weak pull-up resistor.

GPA2 19 23 I/O Bidirectional I/O pin. Can be enabled for interrupt-on-change and/or internal weak pull-up resistor.

GPA3 20 24 I/O Bidirectional I/O pin. Can be enabled for interrupt-on-change and/or internal weak pull-up resistor.

GPA4 21 25 I/O Bidirectional I/O pin. Can be enabled for interrupt-on-change and/or internal weak pull-up resistor.

GPA5 22 26 I/O Bidirectional I/O pin. Can be enabled for interrupt-on-change and/or internal weak pull-up resistor.

GPA6 23 27 I/O Bidirectional I/O pin. Can be enabled for interrupt-on-change and/or internal weak pull-up resistor.

GPA7 24 28 I/O Bidirectional I/O pin. Can be enabled for interrupt-on-change and/or internal weak pull-up resistor.

EP

29

—

— Exposed Thermal Pad. Either connect to VSS, or leave unconnected.

2005-2016 Microchip Technology Inc.

DS20001952C-page 11