SPCA701A 查看數據表(PDF) - Unspecified

零件编号

产品描述 (功能)

生产厂家

SPCA701A Datasheet PDF : 16 Pages

| |||

Preliminary

SPCA701A

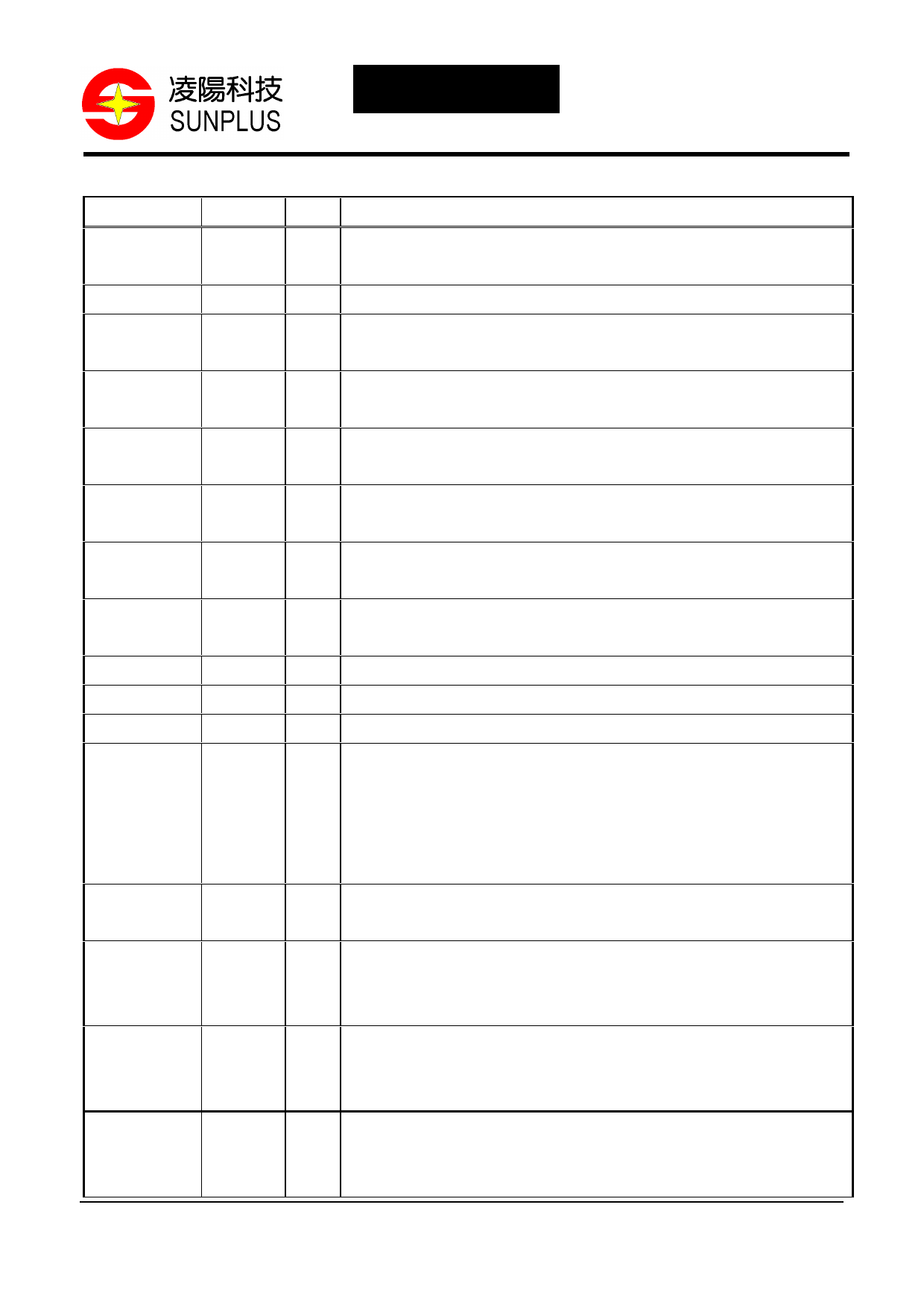

PIN DESCRIPTION (Table 1.)

Mnemonic PIN No. Type

Description

DATA[7:0]

21-28

I YCrCb pixel inputs. They are latched on the rising edge of CLK. YCrCb

input data conform to CCIR 601.

CLK

29

I Pixel clock input.

VSYNC

32

I/O Vertical sync input/output. VSYNC is latched/output following the rising

edge of CLK.

HSYNC

1

I/O Horizontal sync input/output. HSYNC is latched/output following the

rising edge of CLK.

MASTER

16

I Master/slave mode selection. A logical high for master mode operation.

A logical 0 for slave mode operation

CBSWAP

15

I Cr and Cb pixel sequence configuration pin. A logic high swap the Cr

and Cb sequence.

SVIDEO

14

I SVIDEO select input pin. A logic high selects Y/C output. A logic low

selects composite video output.

SLEEP

13

I Power save mode. A logic high on this pin puts the chip into power-

down mode.

Mode[3:2]

17-18

I Mode configuration pin.

Mode[1:0]

19-20

I Useless pins. It will be better to connect them to VDD or DGND.

TEST

2

I Test pin. These pins must be connected to DGND.

VREFIN

9

I Voltage reference input. An external voltage reference must supply

typical 1.235V to this pin. A 0.1 F ceramic capacitor must be used to

de-couple this input to GND. The decoupling capacitor must be as

closed as possible to minimize the length of the load. This pin may be

connected directly to VREFOUT.

VREFOUT

8

O Voltage reference output. It generates typical 1.2V voltage reference

and may be used to drive VREFIN pin directly.

FSADJ

5

- Full-Scale adjust control pin. The Full-Scale current of D/A converters

can be adjusted by connecting a resistor (RSET) between this pin and

ground.

COMP

6

- Compensation pin. A 0.1 F ceramic capacitor must be used to bypass

this pin to VAA. The lead length must be kept as short as possible to

avoid noise.

CVBSY

4

O Composite/Luminance output. This is a high-impedance current source

output. The output format can be selected by the PAL pin. The

CVBSY can drive a 37.5 load. If unused, this pin must be connected

Sunplus Technology Co., Ltd.

2

Rev.: 0.2 1999.12.07