VSC7217UC 查看數據表(PDF) - Vitesse Semiconductor

零件编号

产品描述 (功能)

生产厂家

VSC7217UC Datasheet PDF : 36 Pages

| |||

VITESSE

SEMICONDUCTOR CORPORATION

Preliminary Datasheet

VSC7217

Multi-Gigabit Interconnect Chip

mary or redundant serial input as the data source for that channel. When RXP/RC is HIGH, the C channel serial

data source is PRXC. When LBENn(1:0)=10, the channel’s transmitter is looped back and becomes the serial

data source regardless of the state of RXP/Rn (see Table 4).

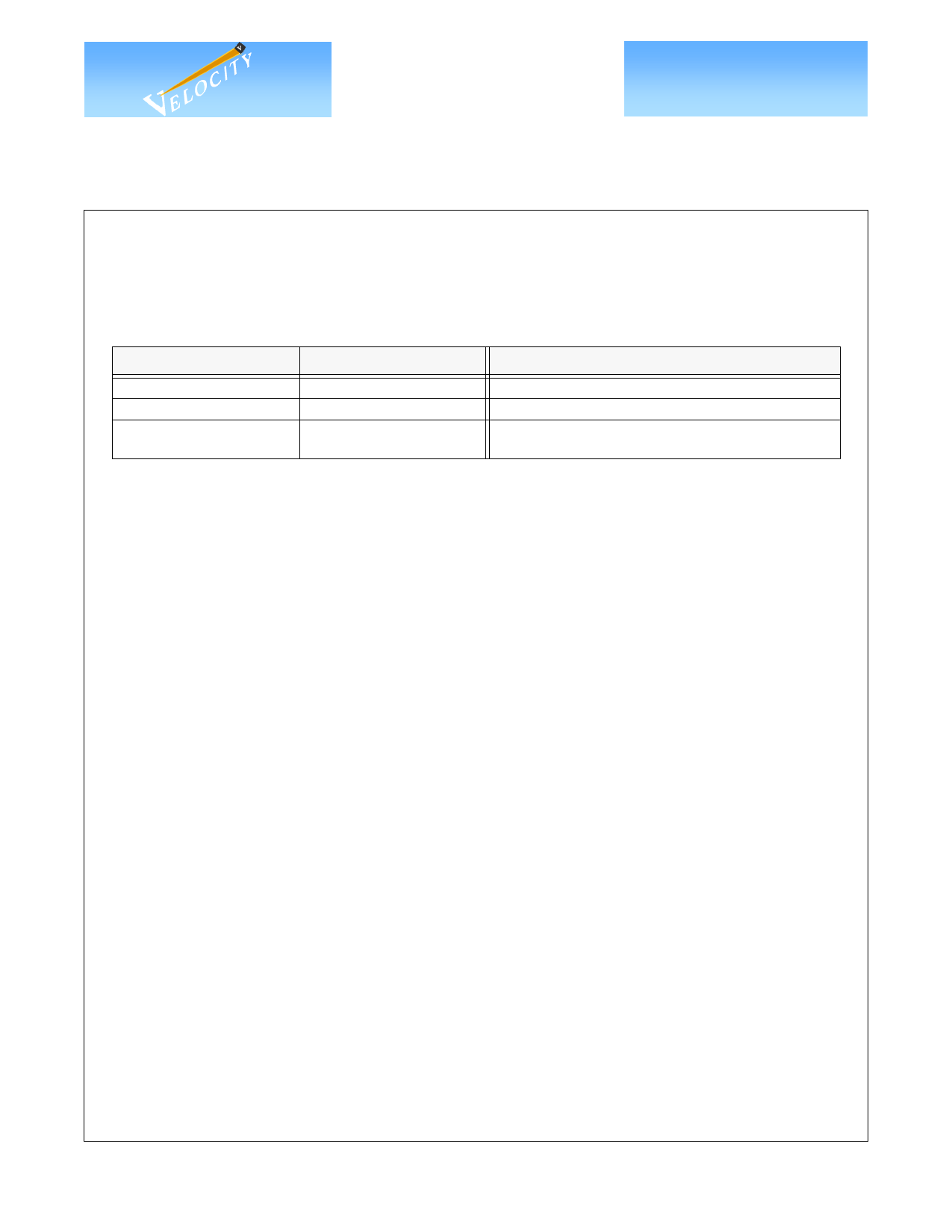

Table 4: Serial Data Source Selection

LBENn(1:0)

≠10

≠10

RXP/Rn

0

1

=10

X

Serial Data Source

RRXn

PRXn

LBTXn

Loopback fromTransmitters

Signal Detection

Each channel’s primary and redundant PECL input buffers have an associated signal detect output,

PSDETn and RSDETn. All eight outputs are available for continuous monitoring of both the selected and non-

selected input. Each signal detect output is asserted HIGH when transitions are detected on the associated PECL

input and the signal amplitude exceeds 200 mV. A LOW indicates that either no transitions are detected or the

signal amplitude is below 100mV. The signal detect outputs are considered undefined when the signal ampli-

tude is in the 100mV to 200 mV range. The signal detect circuitry behaves like a re-triggerable one shot that is

triggered by signal transitions, and whose time-out interval ranges from 40 to 80 bit times. The transition den-

sity is not checked to ensure that it corresponds to a valid Fibre Channel data stream. The PSDETn and

RSDETn output timing is identical to the low-speed receiver outputs, as selected by RMODE(1:0) in Table 5.

Receiver Equalization

Incoming data on the PRX/RRX inputs typically contains a substantial amount of Inter Symbol Interfer-

ence (ISI) or deterministic jitter which reduces the ability of the receiver to recover data without errors. An

equalizer has been added to each of the receiver’s input buffers in order to compensate for this deterministic jit-

ter. This circuit has been designed to effectively reduce the ISI commonly found in copper cables or backplane

traces due to low frequencies traveling faster than high frequencies as a result of the skin effect. The equalizer

boosts high-frequency edge response in order to reduce the adverse effects of ISI.

Clock and Data Recovery

At the receiver, each channel contains an independent Clock Recovery Unit (CRU) that accepts the selected

serial input source, extracts the high-speed clock and retimes the data. Each CRU automatically locks on data

and if the data is not present, will automatically lock to the REFCLK. This maintains a very well-behaved

recovered clock (RCLKn/RCLKNn) which does not contain any slivers and will operate at a frequency of the

REFCLK reference ±200 ppm. The use of an external Lock-to-Reference pin is not needed.

The Clock Recovery Unit must perform bit synchronization which occurs when the CRU locks onto and

properly samples the incoming serial data as described in the previous paragraph. When the CRU is not locked

onto the serial data, the 10-bit data out of the decoder is invalid which results in numerous 8B/10B decoding

errors or disparity errors. When the link is disturbed (the cable is disconnected or the serial data source is

switched), the CRU will require a certain amount of time to lock onto data which is specified in the AC timing

specifications for “Data Acquisition Lock Time.”

G52325-0, Rev. 3.0

6/14/00

© VITESSE SEMICONDUCTOR CORPORATION

741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896

Page 7