SIW3500GIG1 查看數據表(PDF) - RF Micro Devices

零件编号

产品描述 (功能)

生产厂家

SIW3500GIG1 Datasheet PDF : 18 Pages

| |||

Preliminary

SiW3500

EEPROM is not required for configurations with external flash. The EEPROM is the non-volatile memory (NVM) in the

system and contains the system configuration parameters such as the Bluetooth device address, the CODEC type, as

well as other parameters. These default parameters are set at the factory, and some parameters will change depending

on the system configuration. Optionally, the memory parameters can be downloaded from the host processor at boot up

eliminating the need for EEPROM. Please consult the Application Support team for details. The EEPROMs should have

a serial I2C interface with a minimum size of 2 Kbits and 16-byte page write buffer capabilities.

General System Requirements

System Reference Clock

The SiW3500 chip can use either an external crystal or a reference clock as the system clock input. A partial list of

supported frequencies (in MHz) includes: 9.6, 12, 12.8, 13, 14.4, 15.36, 16, 16.8, 19.2, 19.68, 19.8, 26, 32, 38.4, and 48.

For other frequencies, please contact Applications Support. The system reference crystal/clock must have an accuracy

of ±20 PPM or better to meet the Bluetooth specification.

Low Power Clock

For the Bluetooth low power clock, a 32.768 kHz crystal can be used to drive the SiW3500 oscillator circuit, or alterna-

tively, a 32.768 kHz reference clock signal can be used instead of a crystal. If the lowest power consumption is not

required during low-power modes such as sniff, hold, park, and idle modes, the 32.768 kHz crystal may be omitted in the

design.

If the 32.768 kHz clock source is used, the clock source should be connected to the CLK32_IN pin and must meet the

following requirements:

• For AC-coupled via 100 pF or greater (peak-to-peak voltage):

400 mVP-P < CLK32_IN < VDD_C

• For DC-coupled:

CLK32_IN minimum peak voltage < VIL

CLK32_IN maximum peak voltage > VIH

Where VIL = 0.3 * VDD_C

Where VIH = 0.7 * VDD_C

• For both cases, the signal is not to exceed:

-0.3 V < CLK32_IN < VDD_C + 0.3 V

Power Supply Description

The SiW3500 operates at 1.8 V core voltage for internal analog and digital circuits. The chip has internal analog and

digital voltage regulators simplifying power supply requirements to the chip. The internal voltage regulators can be

supplied directly from a battery or from other system voltage sources. Optionally, the internal regulators can be by-

passed if 1.8 V regulated source is available on the system.

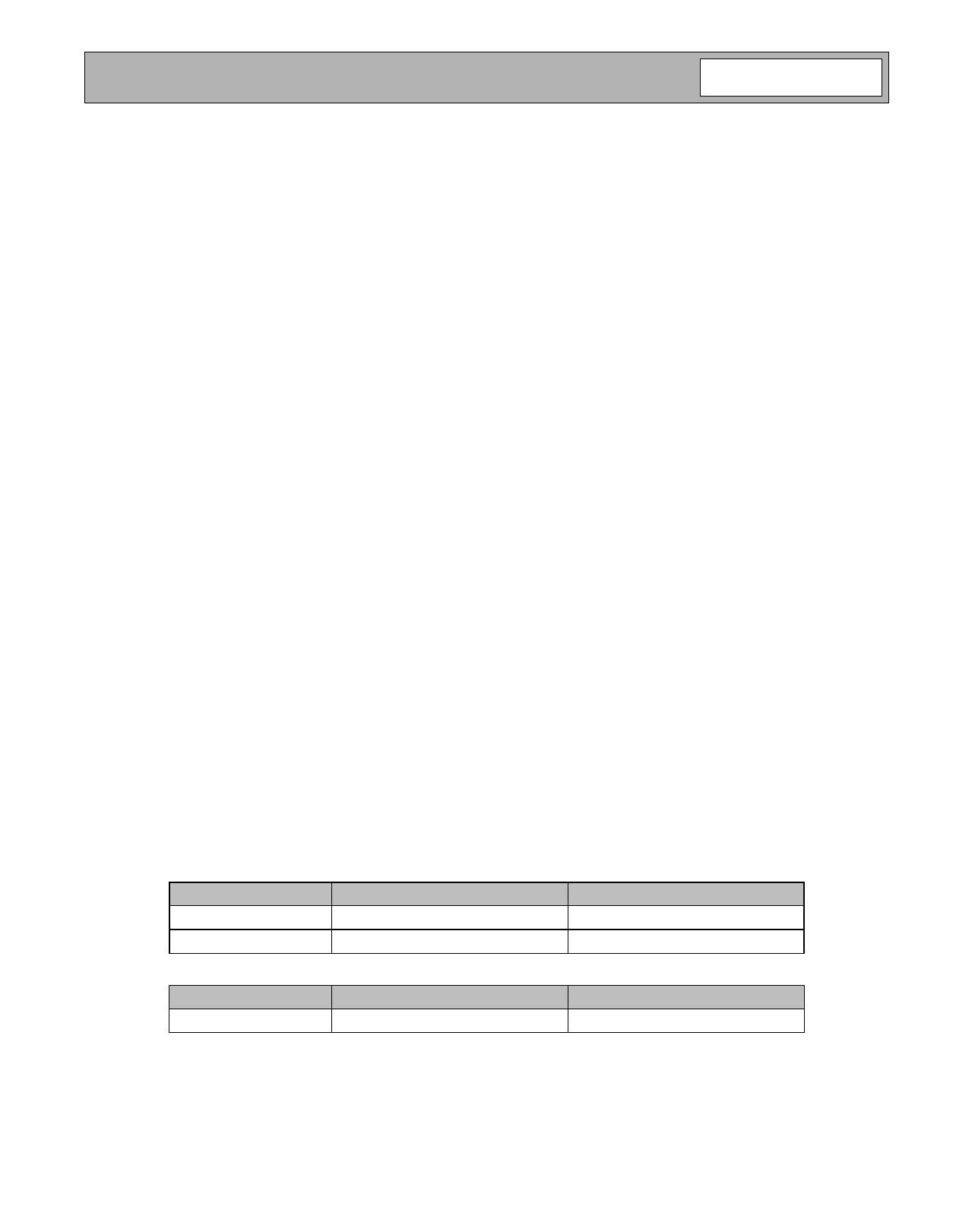

Function

Regulator input pin

Regulator output pin

Internal Regulator Used

Internal Analog Regulator

VBATT_ANA = 2.3 to 3.63 V

VCC_OUT = 1.8 V

Internal Digital Regulator

VBATT_DIG = 2.3 to 3.63 V

VDD_C = 1.8 V

Function

Analog Core Circuits

Circuit voltage supply pin

VCC = 1.8 V

Internal Regulator Bypassed

Digital Core Circuits

VDD_C = 1.8 V

Note: Both regulators can be bypassed if external regulation is desired. When bypassing the analog regulator, the VBATT_ANA and VCC_OUT pins

must be tied together and the external analog voltage (1.8 V) should be applied to the VBATT_ANA pin. When bypassing the digital regulator, the

VBATT_DIG pin should be left unconnected and the external digital voltage (1.8 V) should be applied to VBB_OUT pin.

The power for the I/Os is taken from two separate sources (VDD_P and VDD_P_ALT). They can range from 1.62 to 3.63

60 0066 R00Hrf SiW3500 Radio Processor DS

14-41