HYB39S256160T-8B 查看數據表(PDF) - Infineon Technologies

零件编号

产品描述 (功能)

生产厂家

HYB39S256160T-8B Datasheet PDF : 46 Pages

| |||

HYB39S256400/800/160T

256MBit Synchronous DRAM

When the previous burst is interrupted, the remaining addresses are overridden by the new address

with the full burst length. An interrupt which accompanies an operation change from a read to a write

is possible by exploiting DQM to avoid bus contention.

When two or more banks are activated sequentially, interleaved bank read or write operations

are possible. With the programmed burst length, alternate access and precharge operations on two

or more banks can realize fast serial data access modes among many different pages. Once two or

more banks are activated, column to column interleave operation can be performed between

different pages.

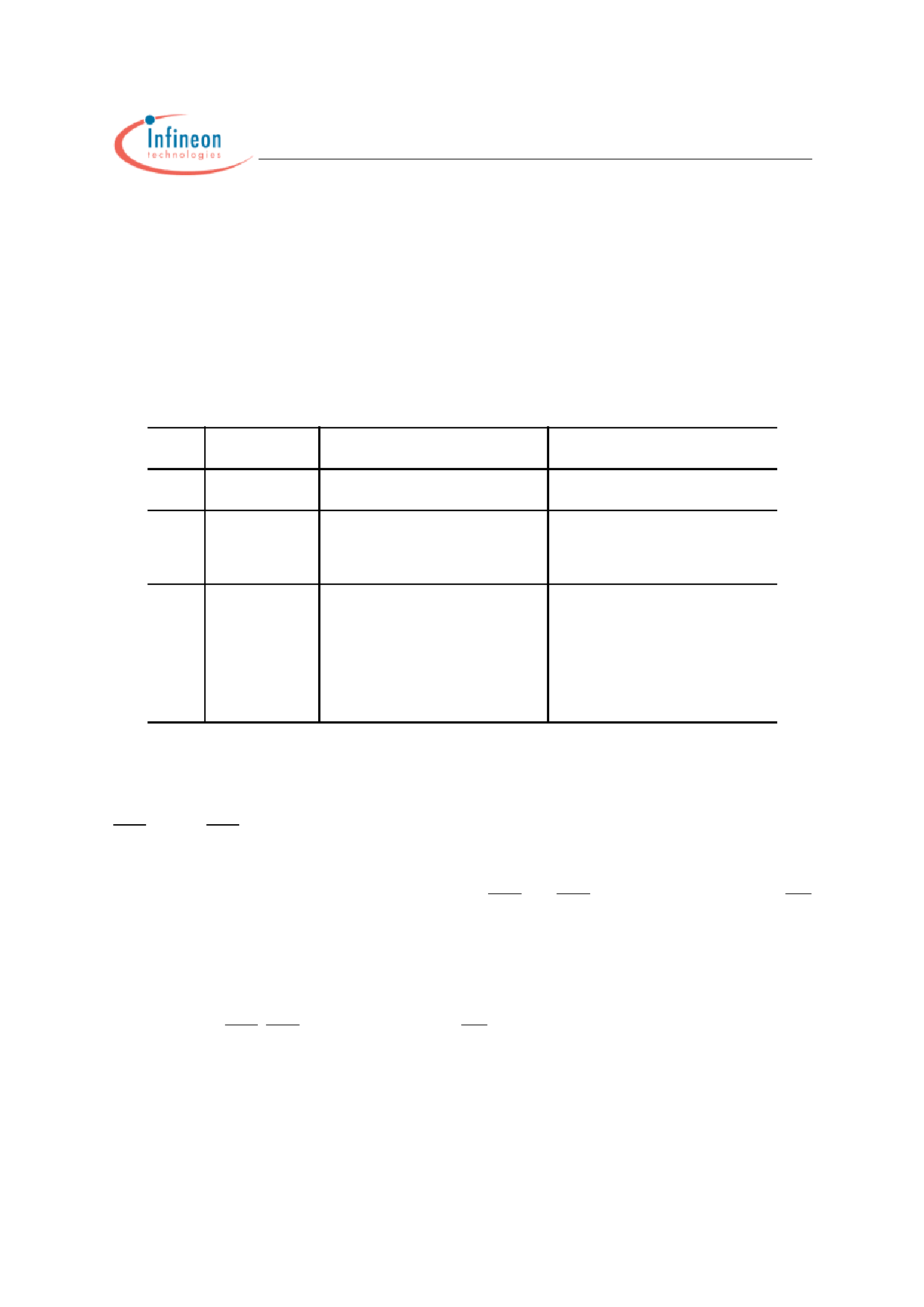

Burst Length and Sequence:

Burst Starting Address Sequential Burst Addressing

Length

(A2 A1 A0)

(decimal)

2

xx0

0, 1

xx1

1, 0

4

x00

x01

x10

x11

0, 1, 2, 3

1, 2, 3, 0

2, 3, 0, 1

3, 0, 1, 2

8

000

001

010

011

100

101

110

111

01234567

12345670

23456701

34567012

45670123

56701234

67012345

70123456

Interleave Burst Addressing

(decimal)

0, 1

1, 0

0, 1, 2, 3

1, 0, 3, 2

2, 3, 0, 1

3, 2, 1, 0

01234567

10325476

23016745

32107654

45670123

54761032

67452301

76543210

Refresh Mode

SDRAM has two refresh modes, Auto Refresh and Self Refresh. Auto Refresh is similar to the

CAS -before-RAS refresh of conventional DRAMs. All of banks must be precharged before applying

any refresh mode. An on-chip address counter increments the word and the bank addresses and no

bank information is required for both refresh modes.

The chip enters the Auto Refresh mode, when RAS and CAS are held low and CKE and WE

are held high at a clock timing. The mode restores word line after the refresh and no external

precharge command is necessary. A minimum tRC time is required between two automatic

refreshes in a burst refresh mode. The same rule applies to any access command after the

automatic refresh operation.

The chip has an on-chip timer and the Self Refresh mode is available. The mode restores the

word lines after RAS, CAS, and CKE are low and WE is high at a clock timing. All of external control

signals including the clock are disabled. Returning CKE to high enables the clock and initiates the

refresh exit operation. After the exit command, at least one tRC delay is required prior to any access

command.

DQM Function

INFINEON Technologies

11