AD9805 查看數據表(PDF) - Analog Devices

零件编号

产品描述 (功能)

生产厂家

AD9805 Datasheet PDF : 24 Pages

| |||

RED

VINR

CDS

PGA

GREEN

VING

CDS

PGA

BLUE

VINB

CDS

PGA

AD9807/AD9805

AD9807/AD9805

VREF

OFFSET<M:0>

GAIN<N:0>

BANDGAP

REFERENCE

8-10

12-10/10-8

I/O

MUX

3

12

DIGITAL 12 DIGITAL

12

12-BIT/10-BIT

–

X

A/D

SUBTRACTOR

MULTIPLIER

INPUT OFFSET

8

REGISTER

CONFIGURATION

REGISTER

R

G

CONFIGURATION

B

REGISTER

2

R

RODD

REVEN

G

GODD GEVEN

B

BODD

BEVEN

MPU

PORT

OEB

12

DOUT<11:0>/MPU<7:0>

CSB

RDB

WRB

A2

A1

A0

CDSCLK1 CDSCLK2 STRTLN ADCCLK

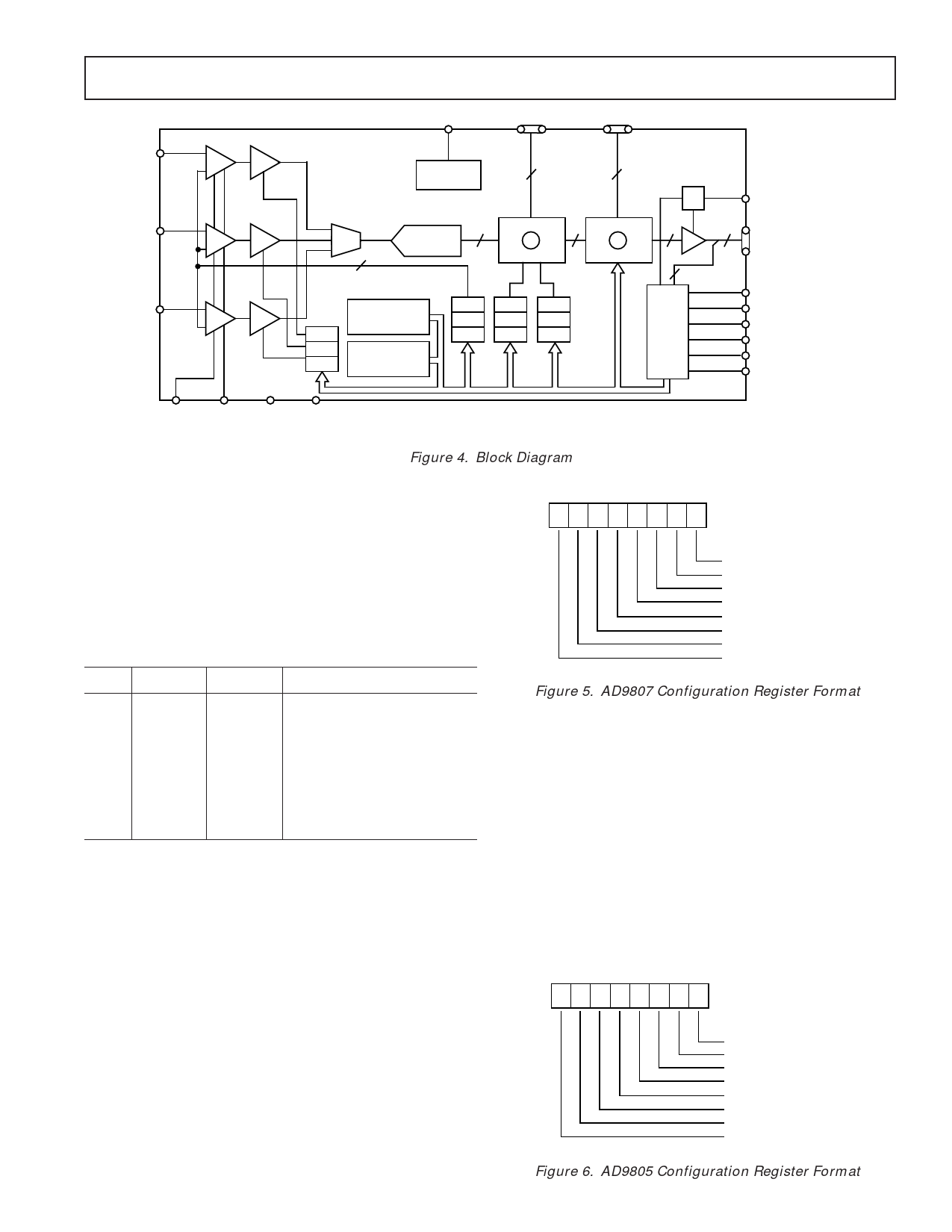

Figure 4. Block Diagram

REGISTER OVERVIEW

MPU Port Map

Table II shows the MPU Port Map. The MPU Port Map is

accessed through pins A0, A1 and A2 of the AD9807/AD9805,

and provides the decoding scheme for the various registers of

the AD9807/AD9805. When writing or reading from any of the

registers, the appropriate bits must be applied to A0–A2.

Table II. MPU Port Map Format

A2

A1

A0

Register

0

0

0

Configuration Register

0

0

1

Configuration Register 2

0

1

0

PGA Gain Register

0

1

1

Odd Offset Register

1

0

0

Even Offset Register

1

0

1

Input Offset Register

1

1

0

RESERVED

1

1

1

Bayer Mode

Configuration Register/AD9807

The Configuration Register controls three functions: a color

pointer, gain and offset pin configurations, and digital gain

scaling. Figure 5 shows the AD9807 Configuration Register.

Bits 0–2 control the digital scaling function. Setting a bit makes

the corresponding condition true. Resetting Bits 0–2 disables

and bypasses the digital multiplier. Bits 3–5 control the gain

and offset pin distribution. Resetting Bits 3–5 disables and

bypasses the digital subtracter and sets the gain word width to

12. Setting any bit makes the corresponding condition true. For

example, if Bit 3 is set, the 2 LSBs of the gain word become the

2 MSBs of the offset word. If Bit 4 is set, the LSB of the gain

word becomes MSB of the offset word. Bits 6 and 7 direct

register data written to the MPU<7:0> bus to the appropriate

red, green or blue register.

76 54 3 21 0

8X FULL SCALE

4X FULL SCALE

2X FULL SCALE

10-BIT GAIN, 10-BIT OFFSET

11-BIT GAIN, 9-BIT OFFSET

12-BIT GAIN, 8-BIT OFFSET

COLOR0

COLOR1

Figure 5. AD9807 Configuration Register Format

Configuration Register/AD9805

The Configuration Register controls three functions: a color

pointer, gain and offset pin configurations, and digital gain

scaling. Figure 6 shows the AD9805 Configuration Register.

Bits 0–2 control the digital scaling function. Setting a Bit

makes the corresponding condition true. Resetting Bits 0–2

disables and bypasses the digital multiplier. Bits 3–5 control

the gain and offset pin distribution. Resetting Bits 3–5 disables

and bypasses the digital subtracter and sets the gain word width

to 10. Setting any bit makes the corresponding condition true.

If Bit 3 is set, the 2 LSBs of the gain word become the 2 MSBs

of the offset word. If Bit 4 is set, the LSB of the gain word

becomes MSB of the offset word. Bits 6 and 7 direct register

data written to the MPU<7:0> bus to the appropriate red,

green or blue register.

76 54 3 21 0

8X FULL SCALE

4X FULL SCALE

2X FULL SCALE

8-BIT GAIN, 10-BIT OFFSET

9-BIT GAIN, 9-BIT OFFSET

10-BIT GAIN, 8-BIT OFFSET

COLOR0

COLOR1

REV. 0

Figure 6. AD9805 Configuration Register Format

–11–