HI-6011 查看數據表(PDF) - Holt Integrated Circuits

零件编号

产品描述 (功能)

生产厂家

HI-6011 Datasheet PDF : 13 Pages

| |||

HI-6011

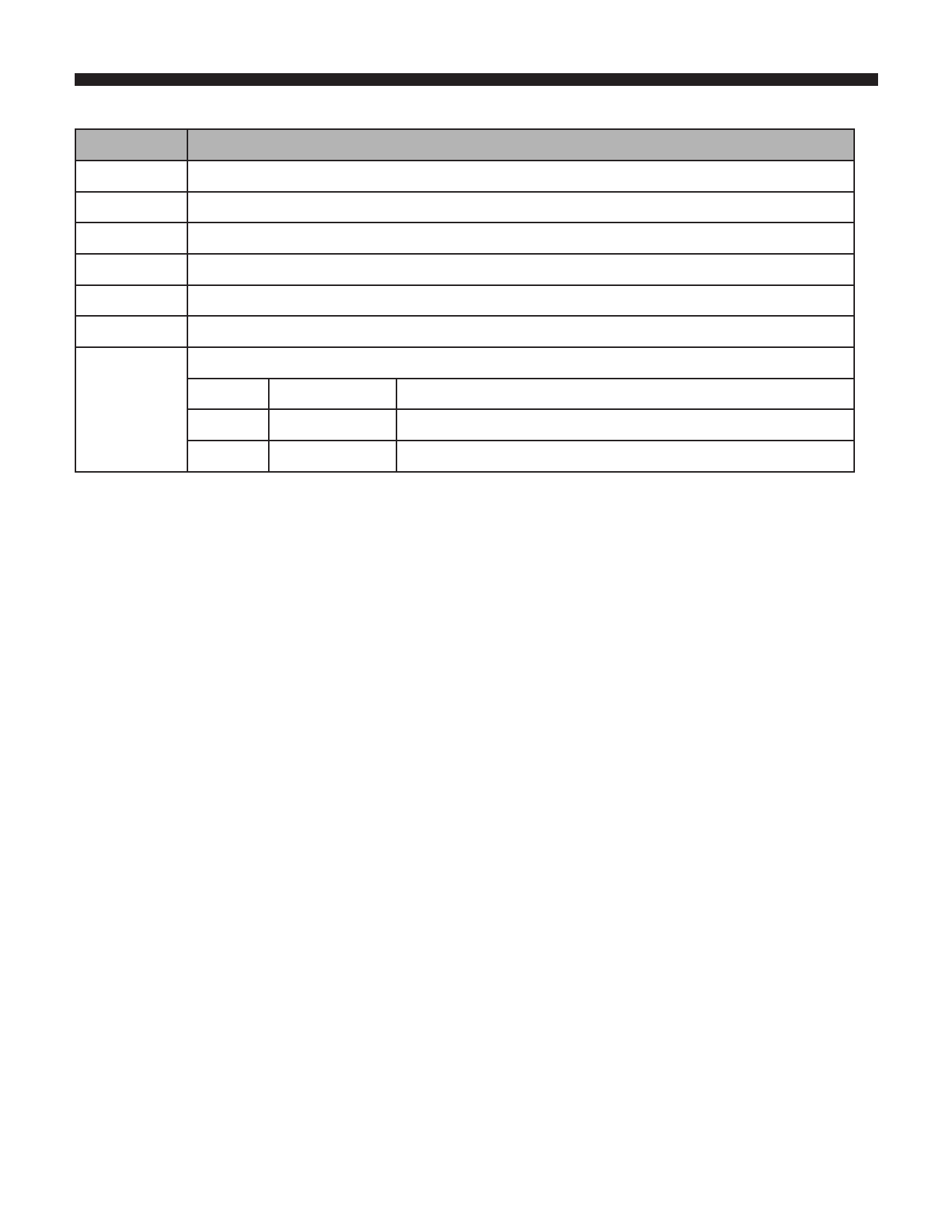

Transmitter/General Status Register

Bits

0

1

2

3

4

5

7:6

Description

XMIT Data.

XMIT Clock (Data changes on the rising edge).

Parity Sense (1 = ODD, 0 = EVEN).

Receiver 1 data rate: 0 = LOW (12-14.5 kbps); 1 = HIGH (100 kbps).

Same as bit 3 for receiver 2.

Transmitter Data Rate: 0 = LOW (12-14.5 kbps); 1 = HIGH (100 kbps).

Input Clock Selection

00 12 MHz

01 6 MHz

1x 1 MHz

RECEIVER OPERATION

Mode 0 Operation

This mode is established by presetting the receiver’s ID label to 00H. In this mode the receiver accepts all data words

transmitted to it. The receiver calculates incoming parity, compares it to the received parity bit and provides a status

bit to indicate the correctness of the received parity. Any premature (before 32 bits are received) idle line condition

resets the receiver and sets a status bit which is retained until a full word is received or until a reset is issued. Receipt

of a full 32-bit word activates the interrupt and sets a status bit.

A 2μs open drain negative pulse is produced as an interrupt to the processor to indicate a full word has been received.

The processor responds to the interrupt by reading interrupt status to determine what event caused the interrupt,

to determine correctness of parity (if applicable) and to react to transmitter state. To read a received word, four

successive reads are required. The first brings bits 1-8 to the data bus, the second brings bits 9-16, etc. A reset for the

receiver being handled may be issued after reading the data, if such reset occurs before the first bit of the next word

is received. If another read of the receiver data is issued after a reset, the most recent received word will again be

read (until another word is received and the receive interrupt and corresponding status bits are thereby re-activated).

In mode 0, if another word is received before the current one has been read, the most recent word received replaces

the previous unread one and causes another receive interrupt. This allows the processor a maximum of 2.2 ms (14.5

kpbs) or 0.32 ms (100 kbps) to respond to assure no loss of data if there is full speed throughput.

In Mode 0, the processor must read the received word before the next received word’s parity bit (bit 32) arrives. If a

read of one word is in progress during the end of the receiving procedure (bits 32, 33) of the next word, data may not

be correct.

Mode 1 Operation:

Any non-zero byte written to a receiver’s ID label register activates this mode and causes a receiver reset. Mode 1

functions identically to mode 0 except that the interrupt is generated only if the address label of the received word

matches that of the preset ID label. Also, if the interrupt for the received word has not been handled by the time a

subsequent word arrives, the first received word is retained. Retention is indefinite (until a reset is issued).

HOLT INTEGRATED CIRCUITS

8