IR3871MPBF 查看數據表(PDF) - International Rectifier

零件编号

产品描述 (功能)

生产厂家

IR3871MPBF

IR3871MPBF Datasheet PDF : 21 Pages

| |||

CIRCUIT DESCRIPTION

PWM COMPARATOR

The PWM comparator initiates a SET signal

(PWM pulse) when the FB pin falls below the

reference (Vref) or the soft start (SS) voltage.

ON-TIME GENERATOR

The PWM on-time duration is programmed with

an external resistor (RFF) from the input supply

(VIN) to the FF pin. The simplified calculation for

RFF is shown in equation 1. The FF pin is held to

an internal reference after EN goes HIGH. A copy

of the current in RFF charges a timing capacitor,

which sets the on-time duration, as shown in

equation 2.

RFF

VOUT

(1)

1V 20 pF FSW

TON RFF 1V 20 pF (2)

VIN

CONTROL LOGIC

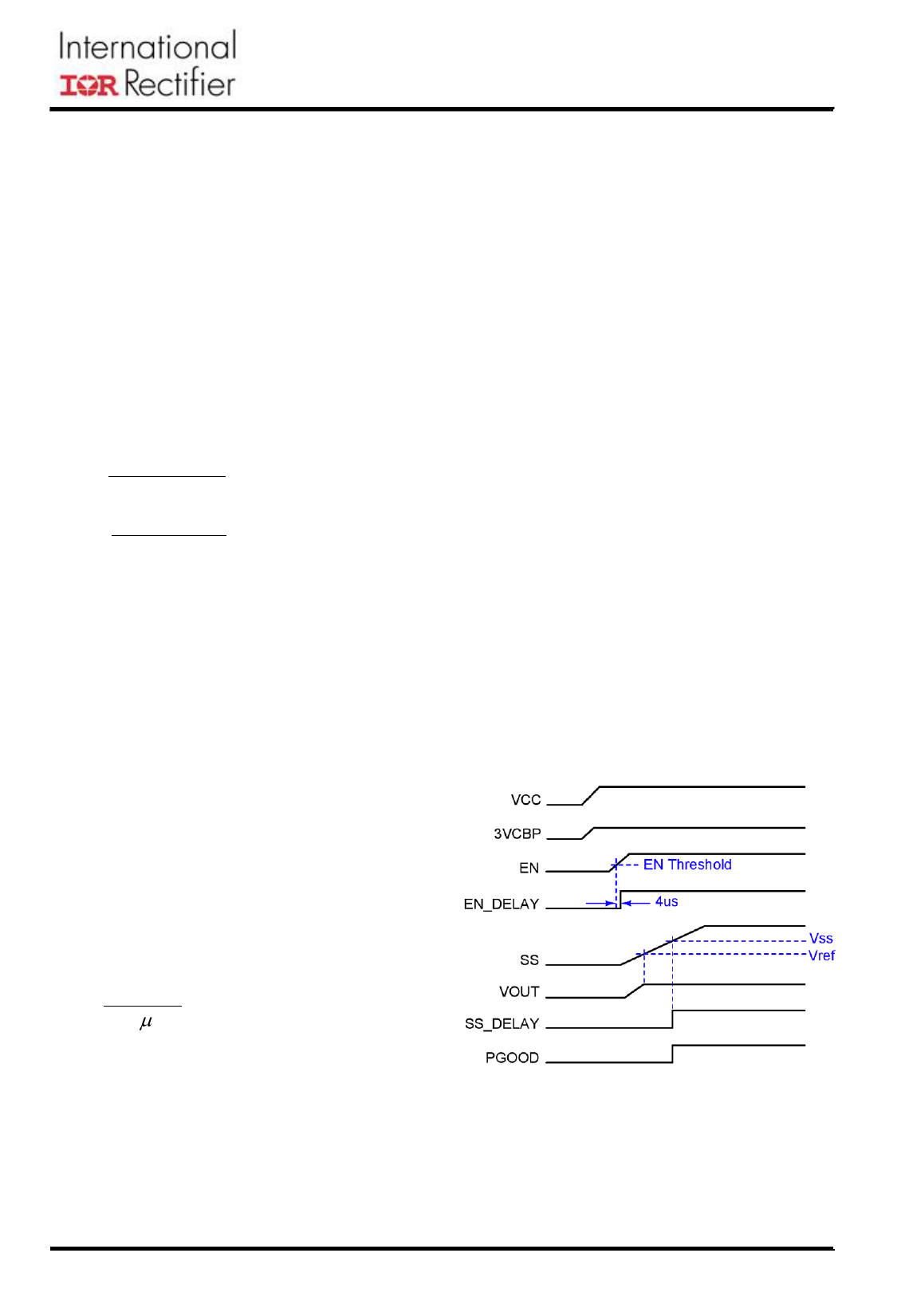

The control logic monitors input power sources,

sequences the converter through the soft-start

and protective modes, and initiates an internal

RUN signal when all conditions are met.

VCC and 3VCBP pins are continuously monitored,

and the IR3871 will be disabled if the voltage of

either pin drops below the falling thresholds.

EN_DELAY will become HIGH when VCC and

3VCBP are in the normal operating range and the

EN pin = HIGH.

SOFT START

With EN = HIGH, an internal 10µA current source

charges the external capacitor (CSS) on the SS pin

to set the output voltage slew rate during the soft

start interval. The soft start time (tSS) can be

calculated from equation 3.

t SS

CSS 0.5V

10A

(3)

The feedback voltage tracks the SS pin until SS

reaches the 0.5V reference voltage (Vref), then

feedback is regulated to Vref. CSS will continue to

be charged, and when SS pin reaches VSS (see

Electrical Specification), SS_DELAY goes HIGH.

With EN_DELAY = LOW, the capacitor voltage

and SS pin is held to the FB pin voltage. A normal

startup sequence is shown in Figure 18.

IR3871MPBF

PGOOD

The PGOOD pin is open drain and it needs to be

externally pulled high. High state indicates that

output is in regulation. The PGOOD logic monitors

EN_DELAY, SS_DELAY, and under/over voltage

fault signals. PGOOD is released only when

EN_DELAY and SS_DELAY = HIGH and output

voltage is within the OV and UV thresholds.

PRE-BIAS STARTUP

IR3871 is able to start up into pre-charged output,

which prevents oscillation and disturbances of the

output voltage.

With constant on-time control, the output voltage

is compared with the soft start voltage (SS) or

Vref, depending on which one is lower, and will

not start switching unless the output voltage drops

below the reference. This scheme prevents

discharge of a pre-biased output voltage.

SHUTDOWN

The IR3871 will shutdown if VCC is below its

UVLO limit. The IR3871 can be shutdown by

pulling the EN pin below its lower threshold.

Alternatively, the output can be shutdown by

pulling the soft start pin below 0.3V.

Figure 18. Normal Startup

11